Si vous demandez quelle interface doit être utilisée pour un SSD prenant en charge le protocole NVMe, alors toute personne (sachant généralement ce qu'est NVMe) répondra : bien sûr PCIe 3.0 x4 ! Certes, il aura très probablement des difficultés avec la justification. Dans le meilleur des cas, nous obtenons la réponse que ces disques prennent en charge PCIe 3.0 x4 et que la bande passante de l'interface est importante. Il a quelque chose, mais toutes les discussions à ce sujet n'ont commencé que lorsque certains disques sont devenus à l'étroit pour certaines opérations dans le cadre du SATA "normal". Mais entre ses 600 Mo/s et (tout aussi théorique) ses 4 Go/s d'interface PCIe 3.0 x4 n'est qu'un gouffre, et rempli d'une tonne d'options ! Et si une seule voie PCIe 3.0 suffisait, puisqu'elle est déjà une fois et demie plus que SATA600 ? Les fabricants de contrôleurs qui menacent de passer au PCIe 3.0 x2 dans les produits économiques, ainsi que le fait que de nombreux utilisateurs n'ont pas tel ou tel, ajoutent de l'huile sur le feu. Plus précisément, théoriquement il y en a, mais vous ne pouvez les libérer qu'en reconfigurant le système ou même en y modifiant quelque chose, ce que vous ne voulez pas faire. Mais je veux acheter un disque SSD haut de gamme, mais on craint qu'il n'y ait aucun avantage (même la satisfaction morale des résultats des utilitaires de test).

Mais est-ce vrai ou pas ? En d'autres termes, est-il vraiment nécessaire de se concentrer exclusivement sur le mode de fonctionnement pris en charge - ou est-il encore possible en pratique principes de sacrifice? C'est ce que nous avons décidé de vérifier aujourd'hui. Que la vérification soit rapide et ne prétende pas à l'exhaustivité, mais les informations reçues devraient suffire (à ce qu'il nous semble) au moins à réfléchir... Mais pour l'instant, familiarisons-nous brièvement avec la théorie.

PCI Express : les normes existantes et leur bande passante

Commençons par ce qu'est le PCIe et à quelle vitesse il fonctionne. On l'appelle souvent un "bus", ce qui est quelque peu incorrect idéologiquement : en tant que tel, il n'y a pas de bus auquel tous les appareils sont connectés. En fait, il existe un ensemble de connexions point à point (semblables à de nombreuses autres interfaces série) avec un contrôleur au milieu et des périphériques connectés (chacun d'entre eux pouvant être un concentrateur de niveau supérieur).

La première version de PCI Express est apparue il y a près de 15 ans. L'orientation pour une utilisation à l'intérieur d'un ordinateur (souvent au sein d'une même carte) a permis de faire le haut débit standard : 2,5 gigatransactions par seconde. Étant donné que l'interface est série et duplex, une seule voie PCIe (x1 ; en fait une unité atomique) peut transférer des données à des vitesses allant jusqu'à 5 Gbit/s. Cependant, dans chaque direction - seulement la moitié de cela, c'est-à-dire 2,5 Gbit / s, et c'est la vitesse complète de l'interface, et non "utile": pour améliorer la fiabilité, chaque octet est codé avec 10 bits, donc la bande passante théorique de une ligne PCIe 1.x est d'environ 250 Mo / s dans chaque sens. En pratique, vous devez toujours transférer des informations de service et, par conséquent, il est plus correct de parler de ≈200 Mo / s de transfert de données utilisateur. Ce qui, cependant, à l'époque, non seulement couvrait les besoins de la plupart des appareils, mais offrait également une marge solide : il suffit de rappeler que le prédécesseur du PCIe dans le segment des interfaces système de masse, à savoir bus PCI, fournissait un débit de 133 Mo/s. Et même si l'on considère non seulement la mise en œuvre de masse, mais également toutes les variantes PCI, le maximum était de 533 Mo / s, et pour l'ensemble du bus, c'est-à-dire qu'un tel PS était divisé en tous les périphériques qui y étaient connectés. Ici, 250 Mo / s (puisque pour le PCI, la bande passante complète et non utile est généralement donnée) par voie - en usage exclusif. Et pour les appareils qui en ont besoin de plus, il était initialement possible d'agréger plusieurs lignes en une seule interface, par puissances de deux - de 2 à 32, c'est-à-dire que l'option x32 fournie par la norme pouvait transférer jusqu'à 8 Go / s dans chacune direction. Dans les ordinateurs personnels, x32 n'a pas été utilisé en raison de la complexité de la création et de la reproduction des contrôleurs et périphériques correspondants, de sorte que l'option avec 16 lignes est devenue le maximum. Il a été utilisé (et est toujours utilisé) principalement par les cartes vidéo, car la plupart des appareils n'en ont pas besoin. En général, un nombre considérable d'entre eux et une ligne suffisent amplement, mais certains utilisent à la fois x4 et x8 avec succès : juste sur le sujet du stockage - contrôleurs RAID ou SSD.

Le temps ne s'est pas arrêté et il y a environ 10 ans, la deuxième version de PCIe est apparue. Les améliorations concernaient non seulement les vitesses, mais aussi à cet égard un pas en avant a été fait - l'interface a commencé à fournir 5 gigatransactions par seconde tout en conservant le même schéma de codage, c'est-à-dire que le débit a doublé. Et encore une fois, il a doublé en 2010 : PCIe 3.0 fournit 8 (et non 10) gigatransactions par seconde, mais la redondance a diminué - 130 bits sont désormais utilisés pour encoder 128 bits, et non 160, comme auparavant. En principe, la version PCIe 4.0 avec le prochain doublement des vitesses est déjà prête à apparaître sur le papier, mais dans un avenir proche, nous ne la verrons guère dans le matériel en grande quantité. En fait, PCIe 3.0 est toujours utilisé en conjonction avec PCIe 2.0 sur de nombreuses plateformes, car les performances de cette dernière ne sont tout simplement... pas nécessaires pour de nombreuses applications. Et là où c'est nécessaire, la bonne vieille méthode d'agrégation de lignes fonctionne. Seul chacun d'entre eux est devenu quatre fois plus rapide au cours des dernières années, c'est-à-dire que PCIe 3.0 x4 est PCIe 1.0 x16, l'emplacement le plus rapide des ordinateurs au milieu des années 2000. Cette option est prise en charge par le haut Contrôleurs SSD, et il est recommandé de l'utiliser. Il est clair que s'il y a une telle opportunité, ce n'est pas suffisant. Et s'il n'y est pas ? Y aura-t-il des problèmes, et si oui, quels sont-ils? C'est avec cette question que nous devons le comprendre.

Méthodologie de test

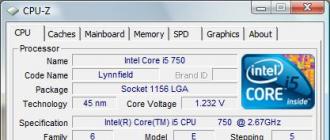

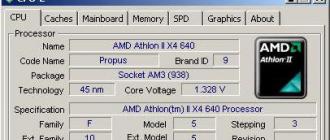

Exécuter des tests avec différentes versions La norme PCIe n'est pas difficile : presque tous les contrôleurs permettent d'utiliser non seulement ceux qu'ils prennent en charge, mais aussi tous les plus anciens. C'est plus difficile avec le nombre de voies : nous voulions tester directement les variantes avec une ou deux voies PCIe. L'Asus H97-Pro Gamer, que nous utilisons habituellement, sur le chipset Intel H97 ne supporte pas l'ensemble, mais outre le slot "processeur" x16 (qui est généralement utilisé), il en possède un autre qui fonctionne en PCIe 2.0 x2 ou x4 modes. Nous avons profité de ce triplet en y ajoutant le mode slot processeur PCIe 2.0, afin d'évaluer s'il y a une différence. Pourtant, dans ce cas, il n'y a pas d'"intermédiaires" tiers entre le processeur et le SSD, mais lorsque vous travaillez avec un emplacement "chipset", il y a : le chipset réel, qui est en fait connecté au même processeur PCIe 2.0 x4. Il était possible d'ajouter quelques modes de fonctionnement supplémentaires, mais nous allions encore faire le gros des recherches sur un système différent.

Le fait est que nous avons décidé de profiter de l'opportunité et de vérifier en même temps une "légende urbaine", à savoir la croyance en l'utilité d'utiliser des processeurs haut de gamme pour tester les lecteurs. Nous avons donc pris le Core i7-5960X à huit cœurs - un parent du Core i3-4170 habituellement utilisé dans les tests (il s'agit de Haswell et Haswell-E), mais qui a quatre fois plus de cœurs. De plus, la carte Asus Sabertooth X99 que l'on trouve dans les bacs nous est utile aujourd'hui par la présence d'un slot PCIe x4, qui en fait peut fonctionner en x1 ou en x2. Dans ce système, nous avons testé trois options x4 (PCIe 1.0 / 2.0 / 3.0) à partir du processeur et du chipset PCIe 1.0 x1, PCIe 1.0 x2, PCIe 2.0 x1 et PCIe 2.0 x2 (dans tous les cas, les configurations de chipset sont marquées sur les schémas avec (c)). Est-il judicieux maintenant de se tourner vers la première version de PCIe, étant donné qu'il n'y a pratiquement pas une seule carte prenant en charge uniquement cette version de la norme qui peut démarrer à partir d'un périphérique NVMe ? D'un point de vue pratique, non, mais pour vérifier a priori le ratio attendu de PCIe 1.1 x4 = PCIe 2.0 x2 et consorts, cela nous sera utile. Si le contrôle montre que l'évolutivité du bus est conforme à la théorie, alors peu importe que nous n'ayons pas encore réussi à obtenir des moyens pratiquement significatifs de connecter PCIe 3.0 x1 / x2 : le premier sera identique à PCIe 1.1 x4 ou PCIe 2.0 x2, et le second - PCIe 2.0 x4 ... Et nous les avons.

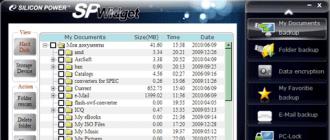

En termes de logiciel, nous nous sommes limités à Anvil's Storage Utilities 1.1.0 : il mesure bien diverses caractéristiques de bas niveau des disques, mais nous n'avons besoin de rien d'autre. Au contraire : toute influence d'autres composants du système est extrêmement indésirable, de sorte que les synthétiques de faible niveau pour nos besoins n'ont pas d'alternative.

Nous avons utilisé un Patriot Hellfire de 240 Go comme "support de travail". Comme il a été constaté lors des tests, il ne s'agit pas d'un record de performances, mais ses caractéristiques de vitesse sont tout à fait cohérentes avec les résultats des meilleurs SSD de même classe et de même capacité. Et il existe déjà des appareils plus lents sur le marché, et il y en aura de plus en plus. En principe, il sera possible de répéter les tests avec quelque chose de plus rapide, cependant, il nous semble que cela n'est pas nécessaire - les résultats sont prévisibles. Mais n'anticipons pas sur nous-mêmes, mais voyons ce que nous avons fait.

Résultats de test

En testant Hellfire, nous avons remarqué que la vitesse maximale sur les opérations séquentielles ne peut en être extraite qu'avec une charge multithread, donc cela devrait également être pris en compte pour l'avenir : la bande passante théorique est pour cela et la théorie " les données, obtenues dans différents programmes selon différents scénarios ne dépendront plus d'elle, mais de ces mêmes programmes et scénarios - dans ce cas, bien sûr, lorsque les circonstances de force majeure n'interfèrent pas :) Nous observons maintenant de telles circonstances : il a déjà été dit plus haut que PCIe 1.x x1 est ≈200 Mo/s, et c'est exactement ce que nous voyons. Deux voies PCIe 1.x ou une PCIe 2.0 sont deux fois plus rapides, et c'est exactement ce que nous voyons. Quatre voies PCIe 1.x, deux PCIe 2.0 ou une PCIe 3.0 sont deux fois plus rapides, ce qui a été confirmé pour les deux premières options, il est donc peu probable que la troisième diffère. C'est-à-dire qu'en principe, l'évolutivité, comme prévu, est idéale : les opérations sont linéaires, Flash les gère bien, donc l'interface compte. Le flash s'arrête réussir vers PCIe 2.0 x4 pour l'enregistrement (ce qui signifie que PCIe 3.0 x2 fera également l'affaire). Lire « peut » est plus, mais la dernière étape donne déjà un gain et demi, et non un double (comme cela devrait potentiellement l’être). Nous notons également qu'il n'y a pas de différence notable entre le chipset et le contrôleur de processeur, et entre les plates-formes également. Cependant, LGA2011-3 est légèrement en avance, mais seulement un peu.

Tout est lisse et beau. Mais les modèles ne se déchirent pas: le maximum dans ces tests n'est que légèrement supérieur à 500 Mo / s, et cela est tout à fait capable même de SATA600 ou (dans l'application aux tests d'aujourd'hui) PCIe 1.0 x4 / PCIe 2.0 x2 / PCIe 3.0x1... C'est vrai : ne soyez pas effrayé par la sortie de contrôleurs économiques pour PCIe x2 ou la présence d'un tel nombre de lignes (d'ailleurs, la version 2.0) dans les slots M.2 sur certaines cartes mères, quand plus n'est pas nécessaire. Parfois, même cela n'est pas nécessaire : les résultats maximum ont été obtenus avec une file d'attente de 16 équipes, ce qui n'est pas typique pour les logiciels de masse. La file d'attente avec 1 à 4 commandes est plus courante, et pour cela, vous pouvez le faire avec une ligne du tout premier PCIe et même du tout premier SATA. Cependant, il y a des frais généraux et ainsi de suite, donc l'interface rapide est utile. Cependant, trop rapide n'est peut-être pas nocif.

Et dans ce test, les plates-formes se comportent différemment et avec une seule file d'attente de commandes - de manière fondamentalement différente. Le "problème" n'est pas du tout que de nombreux cœurs sont mauvais. Ils ne sont de toute façon pas utilisés ici, sauf pour une chose, et pas tellement que le mode boost s'est déroulé avec force et main. Nous avons donc une différence d'environ 20% dans la fréquence des cœurs et une fois et demie dans la mémoire cache - dans Haswell-E, elle fonctionne à une fréquence plus basse, et non de manière synchrone avec les cœurs. En général, la plate-forme haut de gamme ne peut être utile que pour éliminer le maximum de "yops" via le mode multithread maximal avec une grande profondeur de file d'attente de commandes. Le seul regret c'est que du point de vue Travaux pratiques ce sont vraiment des synthétiques sphériques sous vide :)

Pour mémoire, la situation n'a pas fondamentalement changé - dans tous les sens. Mais, ce qui est amusant, sur les deux systèmes, le plus rapide était le mode PCIe 2.0 x4 dans le slot "processeur". Tous les deux! Et avec plusieurs contrôles/recontrôles. À ce stade, vous vous demanderez inévitablement si vous avez besoin ce sont vos nouvelles normes ou vaut-il mieux ne pas se précipiter n'importe où du tout ...

Lorsque l'on travaille avec des blocs de tailles différentes, l'idylle théorique s'effondre sur le fait qu'augmenter la vitesse de l'interface a toujours du sens. Les chiffres obtenus sont tels qu'une paire de voies PCIe 2.0 suffirait, mais en réalité, dans ce cas, les performances sont inférieures à celles de PCIe 3.0 x4, mais pas plusieurs fois. Et en général, la plate-forme haut de gamme "score" ici dans une bien plus grande mesure. Mais de telles opérations se trouvent principalement dans les logiciels d'application, c'est-à-dire que ce schéma est le plus proche de la réalité. En conséquence, il n'est pas surprenant que les interfaces épaisses et les protocoles à la mode ne donnent aucun "effet wow". Plus précisément, ceux qui passent le relais de la mécanique seront donnés, mais exactement la même chose que n'importe quel disque SSD avec n'importe quelle interface fournira.

Total

Pour faciliter la perception de l'image de l'hôpital dans son ensemble, nous avons utilisé le score donné par le programme (total - pour la lecture et l'écriture), ayant effectué sa standardisation selon le mode "chipset" PCIe 2.0 x4 : pour le moment c'est lui qui est le plus largement disponible, puisqu'on le trouve même sur les plateformes LGA1155 ou AMD sans qu'il soit nécessaire de "déformer" la carte vidéo. De plus, il équivaut au PCIe 3.0 x2, que les contrôleurs budgétaires s'apprêtent à maîtriser. Et sur la nouvelle plate-forme AMD AM4, encore une fois, c'est ce mode qui peut être obtenu sans affecter la carte vidéo discrète.

Alors que voyons-nous? L'utilisation de PCIe 3.0 x4, lorsque cela est possible, est certes préférable, mais pas nécessaire : elle apporte littéralement 10 % de performances supplémentaires aux disques milieu de gamme NVMe (dans son segment initialement haut de gamme). Et même alors - en raison d'opérations, en général, pas si courantes dans la pratique. Pourquoi, dans ce cas, cette option particulière est-elle mise en œuvre ? Premièrement, il y avait une telle opportunité, et le stock n'a pas de poche. Deuxièmement, il existe des disques plus rapides que notre test Patriot Hellfire. Troisièmement, il existe des domaines d'activité où les charges « atypiques » pour un système de bureau sont tout simplement assez typiques. Et c'est là que la performance du système de stockage de données est la plus critique, ou du moins la capacité à en faire une partie très rapidement. Mais à l'habitude Ordinateur personnel rien de tout cela ne s'applique.

Comme nous pouvons le voir, l'utilisation de PCIe 2.0 x2 (ou, par conséquent, de PCIe 3.0 x1) n'entraîne pas une diminution spectaculaire des performances - seulement de 15 à 20%. Et ce malgré le fait que dans ce cas nous avons limité par quatre les capacités potentielles du contrôleur ! Pour de nombreuses opérations, cette bande passante est suffisante. Une seule ligne PCIe 2.0 ne suffit plus, il est donc logique que les contrôleurs prennent en charge PCIe 3.0 - et face à un grave manque de lignes dans un système moderne, cela fonctionnera bien. De plus, la largeur x4 est utile - même en l'absence de prise en charge des versions PCIe modernes dans le système, elle vous permettra toujours de travailler à vitesse normale (bien que plus lente qu'elle ne le pourrait potentiellement) s'il y a un slot plus ou moins large .

En principe, un grand nombre de scénarios dans lesquels la mémoire flash réelle s'avère être un goulot d'étranglement (oui, cela est possible et inhérent non seulement à la mécanique), conduit au fait que quatre voies de la troisième version PCIe sur ce lecteur dépasser le premier d'environ 3,5 fois - le débit théorique de ces deux cas diffère 16 fois. D'où, bien sûr, il ne s'ensuit pas que vous deviez vous dépêcher de maîtriser des interfaces très lentes - leur temps est révolu. C'est juste que bon nombre des capacités des interfaces rapides ne peuvent être réalisées qu'à l'avenir. Ou dans les conditions avec lesquelles utilisateur régulier un ordinateur ordinaire n'entrera jamais directement en collision dans la vie (sauf pour ceux qui aiment se mesurer, on sait quoi). En fait, c'est tout.

La technologiePCIExpress 3.0

Dans PCI Express 3.0, la bande passante maximale du canal a été augmentée à 8 GT/s avec des modifications mineures du protocole d'échange, du facteur de forme et des méthodes d'intégrité des données.

Le taux de transfert de données réel pour PCI Express 3.0 est le double de celui de PCI Express 2.0. Les cartes mères prenant en charge PCI Express 3.0 pourront fonctionner avec des cartes graphiques qui consomment jusqu'à 300 W... Une puissance supplémentaire sera consommée via les connecteurs d'alimentation connectés à la carte vidéo. Avoir l'augmentation de la vitesse de transfert des données est due au développement de nouvelles technologies.

C'est pour assurer un débit élevé à une fréquence limitée qu'il a été décidé de passer au schéma de codage 128b130b plus agressif, qui ne prévoit le transfert que de 1,6% d'informations redondantes, contre 20% dans le schéma de codage 8b10b actuel. Le choix de ce principe d'élimination de la redondance au lieu de passer à 10 GT/s était dû au fait que 8 GT/s est le compromis le plus optimal entre coûts, possibilités de production, consommation d'énergie et compatibilité. Il a fallu abandonner l'augmentation de la fréquence à 10 GHz, tout d'abord, pour des raisons de maintien du niveau de consommation électrique dans des limites raisonnables, car l'augmentation de la fréquence s'accompagne d'une augmentation exponentielle de la consommation électrique. Dans le même temps, il est prévu de maintenir la compatibilité mécanique PCIe 3.0 avec les connecteurs utilisés dans les versions antérieures de la norme.

Une augmentation de la fréquence à 8 GHz entraînera une complication importante de la structure des puces, pour la mise en œuvre de laquelle, très probablement, il sera nécessaire d'utiliser au moins un procédé technique de 65 nm. Parmi les autres innovations de la nouvelle norme, nous notons des améliorations de canal, un système de transmission de signal amélioré, une égalisation de la réception et de la transmission et des améliorations du système de boucle à verrouillage de phase.

Dans le cadre de systèmes clé en main, de nouvelles interfaces ont commencé à apparaître en 2011, avec l'accent principal sur les puces graphiques gourmandes en bande passante dans les systèmes de bureau et les serveurs haut de gamme utilisant des cartes Ethernet multiport 10 Gb et Fibre Channel 8 Gb. Quant aux périphériques qui nécessitent une vitesse PCI Express 3.0, ce sont les commutateurs PLX, les contrôleurs Ethernet 40 Gbps, InfiniBand, les périphériques à semi-conducteurs, qui deviennent de plus en plus populaires, et, bien sûr, les cartes vidéo. Les développeurs de PCI Express n'ont pas encore épuisé toutes les innovations possibles, et elles n'apparaissent pas de manière statique, mais dans un flux continu, ce qui ouvre la voie à de nouvelles améliorations dans les futures versions de l'interface PCI Express. Les premières cartes mères et adaptateurs graphiques prenant en charge PCI Express 3.0 sont sortis en 2011.

Prise en charge des canaux virtuels. Mécanisme de canal virtuel, sinon CV (Virtuel Canal) , est la "fondation" pour soutenir divers services au sein de la structurePCI Express... Il permet le déploiement de ressources physiquement indépendantes, qui, avec le marquage du trafic, sont nécessaires pour un traitement optimisé des trafics hétérogènes. Le marquage du trafic est pris en charge par l'utilisation de marqueurs (tags) de la classe de transactions ou, sinon, ST(Transaction Classer) Niveau TLP. La politique exacte pour le trafic hétérogène est réglementée par affichageCT/ CV et par l'arbitrage à laCV... L'affichage de TC / VC dépend des exigences de l'application de la plate-forme. Ces exigences régissent le choix de l'algorithme d'arbitrage VC et la configurabilité/programmabilité des arbitres, ce qui permet un réglage fin de la politique de service de trafic. Les mécanismes de circuit virtuel (VC) traitent les niveaux de détail suivants avec un regard tourné vers l'avenir :

Configurations TC/VC prises en charge ;

Règles et algorithmes d'arbitrage basés sur VC ;

Prise en compte du séquençage du trafic ;

Prise en charge isochrone en tant que modèle personnalisé défini.

Configurations prises en chargeCT/ CV. Un circuit virtuel (VC) est établi lorsqu'une ou plusieurs classes de transaction (TC) s'associent à une ressource VC physique attribuée par l'ID de VC. Chaque classe de trafic prise en charge « Classe de trafic » doit être mappée sur l'un des canaux virtuels. La configuration PCI Express de base (de base) doit prendre en charge la paire par défaut TC0 / VC0, qui est permanente, c'est-à-dire non configurable. Tout support supérieur à ce niveau est facultatif. Le processus de configuration TC / VC est contrôlé par le logiciel système à l'aide d'un modèle de programmation. Pour simplifier l'interopérabilité lors de la configuration de plusieurs circuits virtuels sur une liaison PCI Express, la norme définit des restrictions pour l'ensemble de configurations VC autorisées (correctes). En général, le mappage du trafic vers un canal virtuel autre que TC0 / VC0 est la tâche du logiciel système. Les principales configurations TC/VC sont les suivantes :

Mappage symétrique du trafic vers un lien virtuel ;

Re-mappage du trafic vers un canal virtuel.

Les composants multiports (commutateurs et complexes racine) doivent prendre en charge le mappage TC/VC indépendant pour chaque port PCI Express.

Mécanisme "DispositifSynchronisationArrêter". La modification de la numérotation des bus par le logiciel système pendant le fonctionnement du système peut entraîner une modification de l'ID de l'interrogateur de cet appareil (basé sur les numéros de bus) ; cela pourrait entraîner une modification incorrecte des demandes ou des exécutions pour cet appareil encore en transit pour correspondre à la modification de l'ID du demandeur. Il est également souhaitable de s'assurer qu'aucune transaction sortante ne se produise lors du retrait du dispositif Hot-Plug. Le mécanisme "Device Synchronization Stop" permet au logiciel système de s'assurer qu'il n'y a pas de transactions dans le processus de transfert par rapport à un terminal spécifique jusqu'à ce qu'une opération de renumérotation du bus soit effectuée, ce qui pourrait entraîner une modification du numéro de identifiant du demandeur). L'arrêt synchrone pour les équipements terminaux est mis en œuvre via le mécanisme « Stop » et est associé au bit d'arrêt du registre de commande d'équipement et au bit de transactions en attente du registre d'état de l'équipement. Le logiciel système demande à l'appareil de s'arrêter en définissant le bit d'arrêt dans le registre de commande de l'appareil. Le logiciel considère qu'une opération d'arrêt est terminée si l'appareil signale qu'il n'y a plus de transactions en attente en effaçant le bit Transactions en attente dans le registre d'état de l'appareil ; cependant, il n'est pas interdit à l'appareil d'émettre une nouvelle demande une fois le bit d'arrêt activé. Avant d'effacer le bit Transaction en attente, le terminal doit s'assurer que :

Les exécutions de requêtes sans tampon pour toutes les classes de trafic utilisées ont été acceptées par les demandeurs respectifs ;

Toutes les requêtes initiées par cet appareil ont renvoyé des exécutions ;

Toutes les demandes mises en mémoire tampon de toutes les classes de trafic ont été « vidées/rejetées » (c'est-à-dire acceptées par les cibles visées) dans toutes les directions entre le terminal et le système et entre les terminaux homologues.

Mécanismes de nettoyage / vidange. Dans le cas le plus simple, lorsque le terminal n'est connecté qu'à la mémoire principale, l'effacement peut se faire par lecture dirigée de la mémoire. Les lectures de mémoire doivent être effectuées sur toutes les classes de trafic utilisées par l'appareil. Si le périphérique a des transactions en attente (y compris des exécutions en attente), il doit alors utiliser des transactions sans tampon telles que des lectures de mémoire dirigées adressées à un emplacement homologue spécifique pour le nettoyage. Le mécanisme décrit est spécifique à la mise en œuvre, mais doit être exécuté par le matériel sans la participation de logiciel.

Transactions bloquées. La prise en charge des transactions retardées est nécessaire pour éviter le blocage dans le système lors de l'utilisation d'un logiciel hérité qui initie l'accès aux périphériques d'E/S. Certains processeurs peuvent générer des accès bloqués suite à l'exécution d'instructions qui bloquent implicitement le compteur. Certains logiciels plus anciens appliquent mal ces transactions et génèrent des séquences verrouillées même lorsqu'un accès exclusif n'est pas requis. Étant donné que les accès bloqués aux périphériques d'E/S entraînent des verrous potentiels en plus de ceux mentionnés ci-dessus, ce qui peut entraîner une grave diminution des performances, les points de terminaison PCI Express ne sont pas autorisés à prendre en charge les accès monopole. Les nouveaux logiciels ne doivent pas non plus utiliser d'instructions qui initieraient des accès exclusifs aux périphériques d'E/S. La prise en charge des terminaux pour l'accès exclusif n'a été introduite qu'en raison de problèmes de compatibilité avec les logiciels existants. Seul le complexe racine est autorisé à initier des requêtes PCI Express bloquées. Les requêtes bloquées initiées par les points de terminaison et les ponts ne sont pas prises en charge. Cette cohérence avec les contraintes des transactions bloquées reprend les principes de la « PCILocal Bus Specification » version 2.3. Cette section définit les règles liées à la prise en charge de l'accès exclusif du processeur principal aux points de terminaison hérités, y compris la propagation de ces transactions sur les commutateurs et ponts PCI Express/PCI.

Règles d'initiation et de distribution des transactions bloquées. Les séquences verrouillées sont générées par le ou les processeurs principaux sous la forme d'une ou plusieurs opérations de lecture suivant un nombre égal d'écritures dans la même zone (s). Lorsque l'accès exclusif est établi, tout autre trafic ne peut pas utiliser le chemin entre le complexe racine et le point de terminaison hérité ou le pont bloqué.

Le verrouillage est initié sur PCI Express à l'aide du type "lock" - Read Request / Completion (MRdLk / CplDLk) et se termine par le message "Unlock" (les sémantiques de MRdLk, CplDLk et Unlock ne sont autorisées que pour la classe

trafic par défaut (TCO)).

Le message « Unlock » est diffusé du complexe racine à tous les points d'extrémité et ponts (tout périphérique impliqué dans une séquence verrouillée DOIT ignorer ce message.

L'introduction et la distribution d'une transaction bloquée via PCI Express se fait comme suit :

Les séquences de transactions verrouillées commencent par une requête MRdLk (toutes les lectures séquentielles pour les transactions verrouillées utilisent également des requêtes MRdLk ; les exécutions pour toute requête MRdLk utilisent le type d'exécution CplDLk).

TerminauxHéritagePoint de terminaison. Les points de terminaison hérités ne sont pas autorisés à prendre en charge l'accès exclusif, bien qu'ils puissent être utilisés. Si l'accès exclusif est pris en charge, l'appareil doit le gérer conformément aux règles suivantes :

L'appareil se verrouille lorsqu'il envoie la première exécution de la première requête de lecture exclusive. (une fois qu'un appareil verrouillé doit rester dans cet état jusqu'à ce qu'il reçoive le message « Unlock »);

Lorsqu'il est à l'état bloqué, l'appareil ne doit générer aucune demande à l'aide de classes de trafic mappées sur le circuit virtuel par défaut (VC0) (cette exigence s'applique à toutes les sources possibles de demandes à l'intérieur de l'appareil terminal, dans le cas où il y a plus de une source possible ; les demandes peuvent être générées en utilisant une classe de trafic mappée sur un VC autre que le VC par défaut).

TerminauxPCIExpress. Les points de terminaison PCI Express ne prennent pas en charge l'accès exclusif. Ces dispositifs DOIVENT interpréter les demandes MRdLk comme des demandes non prises en charge.

Réinitialiser les règles pourPCIExpress. Cette section définit le comportement d'une voie PCI Express lors de la réinitialisation. Une réinitialisation peut être générée par une plate-forme ou un composant, mais toute relation entre une réinitialisation de lien PCI Express et une réinitialisation de composant ou de plate-forme est spécifique au composant ou à la plate-forme, respectivement. Il doit y avoir un mécanisme matériel pour régler ou ramener tous les états de port aux conditions initiales définies par la norme - ce mécanisme est appelé Pouvoir Bon Réinitialiser.

Une réinitialisation de l'alimentation qui se produit après la mise sous tension d'un composant est appelée décharge froide ou autrement, Du froid Réinitialiser... Dans certains cas, il est possible de déclencher le mécanisme "Power Good Reset" par le matériel sans retirer et mettre sous tension le composant. Une telle réinitialisation est appelée décharge chaude ou autrement, Chaud Réinitialiser.

Il existe également un mécanisme hors bande pour propager le rinçage hors du canal, il est appelé décharge chaude ou autrement, Chaud Réinitialiser... Le passage à l'état "DL_Inactif" est dans certains cas identique au Hot Reset.

En sortant tout type de réinitialisation(Froid, Chaud ou Chaud), tous les registres de ports et machines à états doivent être mis à leurs états initiaux tels que définis par la normePCI Express.

En quittant l'état Power Good Reset, la couche physique essaiera de démarrer (« augmenter ») le canal. Dès que les deux composants sont entrés dans l'état de la vérification initiale du canal, leur état changera grâce à l'initialisation du canal pour couche physique puis par initialisation pour le canal virtuel VC0, préparant ainsi la couche transaction et la couche liaison à l'utilisation du canal. Après l'initialisation de VC0, les paquets TLP et DLLP peuvent être envoyés sur le canal.

Après une réinitialisation, certains appareils prendront plus de temps avant de pouvoir répondre aux demandes reçues. Les requêtes de configuration nécessitent en particulier que les composants et les périphériques se comportent de manière déterministe qui respecte les règles d'adressage.

Les règles d'adressage requises pour les composants et les appareils se répartissent en deux sous-ensembles :

Exigences relatives aux composants ;

Configuration requise.

Exigences des règles d'adressage pour les composants. Le composant doit entrer dans l'état de vérification de canal actif initial dans les 80 ms après avoir terminé la réinitialisation de l'alimentation. Sur certains systèmes, il est possible que deux composants d'un canal quittent l'état Power Good Reset à des moments différents. Chaque composant doit se conformer à l'exigence d'entrer dans l'état actif initial du test de canal dans les 80 ms après la fin de la Power Good Reset de son point de vue, c'est-à-dire après avoir déterminé que la réinitialisation est terminée. Lors d'une vérification de lien (entrée dans l'état "DL_Active"), le composant doit pouvoir recevoir et traiter les paquets TLP et DLLP.

Exigences d'adressage des règles au système. Pour que le composant d'initialisation interne fonctionne correctement, le logiciel système doit attendre au moins 100 ms après la fin de la réinitialisation (Froid / Chaud / Chaud) avant de permettre la génération de requêtes de configuration vers les périphériques PCI Express. Le système doit s'assurer que tous les composants conçus pour interagir avec le logiciel au démarrage sont prêts à accepter les demandes de configuration dans les 100 ms après la fin de l'état Power Good Reset (la mise en œuvre n'est pas définie par la norme et relève de la responsabilité du développeur) .

Le complexe racine et/ou le logiciel système après réinitialisation (chaud/chaud/froid) doit attendre de l'appareil pour renvoyer l'état « achèvement réussi » pour une demande de configuration correcte 1,0 s. Passé ce délai, l'appareil est considéré comme défectueux. Si le complexe racine répète les demandes de configuration terminées avec le statut « Réessai de la demande de configuration », elles doivent être répétées jusqu'à 1 seconde après l'expiration du temps Torc (délai du complexe racine). À ce stade, le complexe racine peut terminer la demande comme non prise en charge. . Ce délai est similaire au paramètre T rhfa défini pour PCI / PCI-X, et est destiné à fournir une durée adéquate à un périphérique qui doit effectuer sa propre initialisation. Lorsque vous tentez de configurer l'accès aux périphériques du segment PCl ou PCI-X derrière le pont PCI xpress / PCI (PCI -X), le paramètre de temps T rhfa doit être conforme à ces normes.

Règles pour le fonctionnement normal du canal. Si, pour une raison quelconque, le fonctionnement normal du canal diminue, alors la couche de canal et le niveau de transaction entreront dans l'état "DLJnactive". Pour tout pont PCI virtuel ou réel, l'un des événements suivants entraîne la réinitialisation du côté secondaire du pont, en utilisant le mécanisme de la couche physique pour signaler une réinitialisation de lien :

Réglage du bit Réinitialisation du bus secondaire dans le registre Contrôle du pont;

Passage à l'état " DL_ Inactif" sur le côté principal du pont;

Réinitialisation du canal à l'aide d'un mécanisme de couche physique pour la communication " Relier Réinitialiser" .

Certains aspects de Power Good Reset décrits dans la norme PCI Express sont spécifiques à la plate-forme et au facteur de forme. Certaines plates-formes, facteurs de forme ou applications peuvent nécessiter une spécification supplémentaire de la synchronisation et/ou des relations de commande entre les composants du système pour la réinitialisation de l'alimentation. Par exemple, ils peuvent exiger que tous les composants PCI Express du châssis respectent l'état Power Good Reset et sortent en même temps (dans certaines tolérances). Dans un environnement à plusieurs arbres, le corps contenant le complexe racinaire devra peut-être être le dernier à quitter l'état Power Good Reset.

Dans tous les cas où l'alimentation est appliquée, les paramètres de synchronisation suivants doivent être déterminés :

Tpvpgl - le temps minimum pendant lequel le signal PowerGood doit rester inactif après la mise sous tension ;

T pwrgd - temps minimum pendant lequel le signal Power_Good doit être inactif après avoir été effacé ;

fail - après la mise sous tension, le signal Power_Good doit être supprimé dans cet intervalle de temps.

De plus, des paramètres supplémentaires peuvent être définis.

Dans tous les cas où le générateur d'horloge est pris en charge, le paramètre Tpwrgd-clk doit être spécifié - la durée minimale pendant laquelle le signal Power_Good doit rester inactif une fois que toute horloge prise en charge est stable. Des paramètres supplémentaires peuvent également être définis si nécessaire.

Support de mécanismeChaud- Brancher. Les périphériques enfichables à chaud sont essentiels pour garantir un niveau élevé de disponibilité du système. Les technologies d'enfichage à chaud d'aujourd'hui sont coûteuses et posent de nombreux défis découlant de l'ensemble complexe et vulnérable de relations qui existent entre le matériel et les logiciels. Cela entraîne une augmentation des coûts et du temps pour les entreprises. La technologie PCI Express améliore les performances et la disponibilité du système, tout en améliorant considérablement la facilité d'entretien et en réduisant les coûts en standardisant les modèles d'utilisation et en éliminant le recours aux codes des fournisseurs et aux composants matériels pour garantir le fonctionnement fiable des périphériques enfichables à chaud.

La technologie PCI Express résout les problèmes inhérents à la technologie hot-plug conventionnelle des manières suivantes :

PCI Express a été conçu dès le départ pour être enfichable à chaud, de sorte que les registres de contrôle enfichables à chaud font partie de la norme PCI Express (par opposition à SHPC1.0) ;

Le système d'exploitation est fourni avec une interface simple pour accéder aux registres de contrôle matériels hot-plug pour prendre en charge la technologie hot-plug (par opposition aux méthodes précédentes basées sur le BIOS) ;

À condition de caractéristique standard l'enfichage à chaud du matériel, défini à un niveau architectural de base ;

La technologie est basée sur l'architecture Standard Hot-Plug Controller (SHPC).

Les fonctionnalités de conception améliorées améliorent la fiabilité de la plate-forme à des coûts de fabrication OEM relativement bas.

La technologie PCI Express prend en charge l'enfichage à chaud standard en définissant et en exigeant l'allocation de registres appropriés pour contrôler les fonctions liées aux trois couches critiques de la plate-forme, à savoir :

Avec corps

Avec connecteur de bus

Avec terminal (adaptateur)

Cela garantit l'interopérabilité entre les produits de différents fournisseurs. À leur tour, les professionnels de l'informatique et les gestionnaires de centres de données consacrent moins de temps à la formation technique et à la maintenance du système en raison des différences considérablement réduites entre les plates-formes des fournisseurs. De plus, le retour sur investissement est amélioré en éliminant le besoin d'acheter tous les composants du système auprès d'une source unique pour éviter les problèmes de compatibilité.

L'architecture sous-jacente de la technologie PCI Express est basée sur l'architecture SHPC (Standard Hot-Plug Controller) telle que définie dans la spécification PCI Standard Hot-Plug Controller and Subsystem, Révision 1.0. Cette spécification est publiée par le PCI Special Interest Group (PCI SIG) et est disponible sur le site Web PCI-SIG. La technologie PCI Express utilise tous les composants de l'architecture SHPC standard, qui sont résumés dans le tableau ci-dessous. Les colonnes Component Areas représentent les composants de la plate-forme qui implémentent le modèle SHPC.

Bien que la spécification de connexion à chaud PCI définisse les exigences matérielles, elle ne décrit pas un modèle complet pour la gestion des opérations de connexion/déconnexion des périphériques — SHPC 1.0 définit le modèle logiciel requis. Introduit en 2002, PCI Express prend entièrement en charge la technologie d'enfichage à chaud PCI précédente ainsi que le modèle SHPC, et l'utilisation d'une interface de registre simple supprime la dépendance BIOS de l'implémentation de la technologie et l'apporte au système d'exploitation. Essentiellement, la technologie PCI Express élimine le besoin de s'appuyer sur le BIOS ACPI et le pilote de contrôleur hot-plug spécifique à la plate-forme en fournissant une connexion standard à ce contrôleur qui peut être utilisée sur n'importe quelle plate-forme de n'importe quel fournisseur.

La technologie PCI Express tire parti des atouts de l'architecture d'E/S existante tout en répondant aux besoins actuels et futurs avec la possibilité d'activer ou de désactiver la prise en charge des éléments d'extension de manière native dans le système d'exploitation. Cette méthode de gestion, appelée Operating System Hot-Plug (OSHP), doit être prise en charge par un BIOS de plate-forme compatible ACPI. Si la prise en charge de l'extension native est désactivée, le contrôle de connexion à chaud est transmis à l'interface BIOS ACPI. Si la prise en charge de l'extension native du système d'exploitation est activée, le BIOS ACPI n'est pas activé, ce qui permet au système d'exploitation de gérer indépendamment le branchement à chaud des périphériques.

Alors que les technologies PCI Express et SHPC offrent la même fonctionnalité, l'ensemble de registres utilisé pour implémenter la technologie PCI Express est légèrement différent de l'ensemble de registres utilisé pour la norme SHPC ; cependant, le système d'exploitation lui-même peut gérer à la fois SHPC et PCI Express avec quelques modifications mineures à l'interface liée au registre.

La technologie PCI Express prend en charge les périphériques enfichables à chaud pour les solutions modulaires et intégrées. Une amélioration significative que la technologie PCI Express a apportée à la conception existante est le connecteur « mate-last / break-first », qui protège le matériel contre les pannes. L'un des principaux avantages de la technologie d'enfichage à chaud PCI Express par rapport aux modèles précédents est le caractère unique des modules PCI Express - ils sont branchés par le panneau arrière ou avant et ne nécessitent pas d'ouvrir le boîtier.

Les solutions modulaires et intégrées sont basées sur le même modèle logiciel. Le coût de mise en œuvre de diverses options pour les solutions de plate-forme modulaire est nettement inférieur au coût des solutions alternatives proposées précédemment. Les solutions modulaires sont encore moins chères car le contrôleur de puissance a été déplacé vers le module (pas de gestion de l'alimentation côté embase du connecteur) et le coût correspondant est inclus dans le coût total du module. Un avantage supplémentaire d'une solution modulaire est que le coût augmente à mesure qu'elle grandit, ce qui vous permet d'investir progressivement dans la solution au fur et à mesure de sa croissance.

Pour profiter de la plus grande fiabilité à moindre coût que la technologie PCI Express peut offrir, les conditions suivantes doivent être remplies :

Les concepteurs de matériel doivent inclure le support technologique dans leurs nouveaux projets

Les développeurs de logiciels doivent intégrer la prise en charge OSHP dans les nouvelles versions du BIOS et mettre en œuvre un modèle d'utilisation basé sur SHPC ;

Les OEM doivent distribuer des produits de serveur intégrés basés sur des composants prenant en charge la technologie PCI Express ;

Les professionnels de l'informatique et les gestionnaires de centres de données doivent migrer vers des plates-formes basées sur PCI Express pour maximiser les avantages de la technologie hot-plug.

L'architecture PCI Express est conçue pour prendre en charge nativement les périphériques enfichables à chaud et enfichables à chaud (norme client) pour tous les facteurs de forme PCI Express qui prennent en charge les périphériques enfichables à chaud et enfichables à chaud. Ce modèle fournit un cadre pour le comportement des indicateurs et des boutons, s'ils sont implémentés dans le système. La définition des voyants et des boutons s'applique à tous les modèles PCI Express Hot-Plug.

Modèle personnaliséPCIExpressChaud- Brancher. Le modèle d'utilisateur standard, comme son nom l'indique, est principalement destiné aux utilisateurs qui exploitent des systèmes avec des emplacements Hot-Plug. Cet objectif est dû au fait que les systèmes utilisateurs contiennent généralement du matériel et des logiciels de différents fabricants. Le modèle permet aux utilisateurs d'utiliser les emplacements Hot-Plug de leurs systèmes sans recyclage supplémentaire. La norme utilisateur PCI Express Hot-Plug est dérivée de la norme PCI Hot-Plug Controller and Subsystem Specification version 1.0. Ces modèles sont identiques du point de vue de l'utilisateur. Seules des modifications mineures ont été apportées pour enregistrer les définitions et la conformité au modèle personnalisé standard requis par tous les facteurs de forme PCI Express qui implémentent le Hot-Plug et utilisent des LED et des boutons.

Écart de facteur de formePCI. Un écart par rapport au modèle d'utilisateur standard conduit à des solutions PCI-Express incompatibles et se manifestera par des résultats indésirables, tels que :

Complexité de fonctionnement pour l'utilisateur ;

Tests de matériel plus coûteux ;

Incompatibilité fonctionnelle avec le logiciel système ;

Erreurs du logiciel système dues à un comportement du système non testé.

Indicateurs. Le modèle personnalisé standard définit deux indicateurs : indicateur de puissance et indicateur d'attention... La plate-forme peut fournir deux indicateurs dans chaque fente ou panneau de module, les indicateurs peuvent être mis en œuvre sur le châssis ou le module, les détails de mise en œuvre dépendent des exigences du facteur de forme hot-plug. Chaque indicateur est dans l'un des trois états:

Inclus,

Éteindre,

Miroiter.

Le logiciel du système Hot-Plug a un contrôle exclusif sur l'état des indicateurs en raison de la possibilité d'écrire dans le registre de commande associé à l'indicateur. Le port compatible Hot-Plug contrôle le taux de clignotement des LED, le cycle de service et la phase.

Indicateurs clignotants fonctionner à une fréquence de 1 à 2 Hz avec un facteur de marche de 50 % (± 5 %). Les LED clignotantes ne doivent pas être synchronisées et en phase entre les ports.

Les LED doivent être à proximité immédiate de leur emplacement Hot-Plug associé si les LED sont implémentées sur le châssis afin que la connexion entre les LED et l'emplacement Hot-Plug soit aussi lâche que possible.

Les deux indicateurs sont entièrement contrôlés par le logiciel système. Un commutateur ou un périphérique de port racine ne changera jamais l'état du voyant en réponse à un événement tel qu'une panne de courant ou une ouverture soudaine du verrou MRL, à moins que le logiciel système n'envoie spécifiquement une telle commande. Une exception est prévue pour les plates-formes compatibles avec un mécanisme de détection de défaut de contact d'alimentation. Dans ce cas spécifique de panne, la plate-forme est autorisée à « supprimer » le commutateur ou le périphérique du port racine et forcer l'allumage du voyant d'alimentation (pour indiquer que la carte d'extension ne peut pas être retirée). Dans tous les cas, l'état interne du port du voyant d'alimentation doit correspondre à l'état sélectionné par le logiciel. La gestion par le logiciel système des défauts persistants est facultative et n'est pas décrite séparément. Par conséquent, le fabricant de la plate-forme doit s'assurer que cette fonctionnalité supplémentaire du modèle utilisateur standard est exécutée par un logiciel supplémentaire, décrit dans la documentation de la plate-forme ou d'une autre manière.

Indicateur d'attention.Indicateur d'attention "Attention"jaune ou ambré est utilisé pour indications de problèmes fonctionne ou indique que le slot Hot-Plug est en cours d'identification, ce qui permet de localiser son état.

Le voyant d'avertissement est éteint. Lorsque le voyant Attention est éteint, cela signifie que la carte d'extension (si présente) et le slot Hot-Plug fonctionnent normalement et ne nécessitent pas d'attention.

Le voyant Attention est allumé. Si indicateur d'attention "Attention"est allumé, cela signifie qu'il y a un problème avec le fonctionnement de la carte ou du slot. s'entendent comme les conditions qui empêchent la poursuite du fonctionnement de la carte d'extension. Le système d'exploitation ou un autre logiciel système détecte cet état d'une carte d'extension grâce à l'état de l'indicateur d'attention associé. Des exemples de problèmes de performances incluent des problèmes de câbles externes, des cartes d'extension, des pilotes logiciels et des pannes de courant. En général, l'état ON de l'indicateur d'attention signifie qu'une tentative a été effectuée et qu'elle a échoué, ou qu'un événement inattendu s'est produit.

L'indicateur d'attention n'est pas utilisé pour signaler les problèmes rencontrés lors de la validation d'une demande d'opération Hot-Plug. Le terme "validation" s'applique à toute validation effectuée par le logiciel système pour garantir que l'opération demandée ne posera pas de problème. Les exemples d'échecs de validation incluent l'échec d'exécution d'une opération Hot-Plug, une mauvaise distribution de l'alimentation et d'autres conditions qui peuvent être détectées avant le début de l'opération.

Indicateur d'attention clignotant. Un indicateur "Attention" clignotant signifie que le logiciel système identifie cet emplacement à la demande de l'opérateur. Ce comportement est contrôlé par l'utilisateur (par exemple, via l'API ou des contrôles).

Indicateur de puissance.Indicateur d'alimentation a un agréable couleur verte et est utilisé pour indiquer l'état d'alimentation de l'emplacement (Tableau 9).

Le voyant d'alimentation est éteint. Lorsque le voyant d'alimentation est éteint, cela signifie qu'il est permis d'insérer ou de retirer une carte d'extension. L'alimentation principale de l'emplacement est supprimée, si cela est nécessaire pour le facteur de forme, un exemple de suppression de l'alimentation principale est le facteur de forme de la carte PCI Express. Si la plate-forme fournit des Vaux aux emplacements Hot-Plug et que le verrou MRL est fermé, alors tous les signaux commutés par le verrou MRL sont signalés à l'emplacement quel que soit l'état de la LED. Lorsque le verrou MRL est ouvert, les signaux qu'il commute sont supprimés. Le logiciel système doit éteindre le voyant d'alimentation lorsque le logement n'est pas alimenté et/ou autorisé à insérer ou retirer des cartes d'extension. Cette règle est dictée par la spécification électromécanique correspondante pour le facteur de forme.

Le voyant d'alimentation est allumé. Lorsque le voyant d'alimentation est allumé, cela signifie que l'alimentation principale est fournie à l'emplacement et qu'il est interdit d'insérer ou de retirer une carte d'extension.

Indicateur d'alimentation clignotant. Un voyant d'alimentation clignotant indique que l'alimentation est fournie ou supprimée de l'emplacement et que vous n'êtes pas autorisé à installer ou à retirer des cartes d'extension. L'indicateur d'alimentation clignotant fournit également un retour visuel à l'opérateur lorsque le bouton Attention est enfoncé.

Verrou manuelLMR. Le loquet de rétention à commande manuelle (MRL) est un mécanisme de rétention à commande manuelle qui maintient la carte d'extension dans le logement et empêche l'utilisateur de retirer la carte. Ce loquet maintient fermement la carte dans la fente afin que les câbles puissent être connectés sans risque de contact intermittent. Sur les plates-formes qui n'implémentent pas de capteurs MRL, les verrous MRL sont autorisés, qui contiennent deux ou plusieurs cartes d'extension en même temps.

CapteurLMR. CapteurLMR Peut être ligne commutée, optique ou autre appareil tactile lequel indique au port la position du loquetLMR... Le capteur MRL signale « fermé » lorsque le loquet MRL est complètement fermé et « ouvert » dans tous les autres cas (c'est-à-dire, complètement ouvert et toutes les positions intermédiaires). Si l'alimentation Vaux est appliquée aux emplacements Hot-Plug, les signaux de commutation de verrouillage MRL doivent être automatiquement supprimés de l'emplacement si le capteur MRL indique que le verrouillage MRL est ouvert, et les signaux doivent être appliqués à l'emplacement si le capteur MRL indique que le loquet MRL a été refermé. Le capteur MRL permet au port de suivre la position du verrou MRL et détecte donc une ouverture soudaine du verrou MRL. Lorsque l'ouverture soudaine du verrou MRL est associée à un emplacement déjà identifié, le port modifie l'état de cet emplacement en désactivé et en informe le logiciel système. Le port ne modifie pas l'état des voyants d'alimentation et d'attention.

Interverrouillage électromécanique.Verrouillage électromécanique- Ce mécanisme pour le physique blocage de la carte d'extension ou du loquetLMR jusqu'à, jusqu'à ce que le logiciel système et le port le libèrent... Mise en œuvre du verrouillage optionnel, et l'interface logicielle manque d'un mécanisme pour un contrôle précis du verrouillage électromécanique. Le modèle utilisateur standard suppose que lorsque des verrouillages électromécaniques sont mis en œuvre, ils pilotent une sortie de port qui fournit l'alimentation principale à la fente. Les systèmes peuvent étendre davantage la gestion des verrous pour fournir une protection physique aux cartes d'extension.

Bouton Attention.Bouton Attention (Attention Bouton) est un bouton à action instantanée situé à côté de chaque emplacement Hot-Plug ou sur un module, et contrôlé par l'utilisateur pour lancer une opération de retrait à chaud ou de permutation dans un emplacement donné... Indicateur d'alimentation fournit une rétroaction visuelle avec l'opérateur (si le logiciel système accepte la demande initiée par le bouton attention) en vacillant... Dès que le voyant d'alimentation a clignoté, l'utilisateur est informé intervalle de cinq secondes pour annuler, au cours de laquelle un nouvel appui sur le bouton annule l'opération.

Si l'opération initiée par le bouton échoue pour une raison quelconque, il est recommandé que le logiciel système présente un message expliquant l'échec via l'interface utilisateur du logiciel ou l'ajoute au journal système.

Interface utilisateur de programmation. Le logiciel du système doit fournir une interface utilisateur logicielle qui permet de déclencher des opérations d'extraction et de remplacement à chaud et qui permet de suivre l'état d'un port saisi. La discussion détaillée de l'interface utilisateur enfichable à chaud est spécifique au système d'exploitation et n'est donc pas définie dans la norme PCI Express.

Dans les systèmes avec plusieurs emplacements Hot-Plug, le logiciel système doit permettre à l'utilisateur de lancer des opérations dans chaque emplacement quel que soit l'état des emplacements restants. Ainsi, l'utilisateur est autorisé à lancer des opérations Hot-Plug sur un slot en utilisant soit l'interface utilisateur du logiciel, soit le bouton Attention pendant que le Hot-Plug est en cours sur l'autre slot, quelle que soit l'interface qui a été utilisée pour démarrer les premières opérations. .

Fonction de distribution de puissance. Avec l'ajout de cartes d'extension remplaçables à chaud, il est nécessaire que le système alloue correctement l'alimentation à tout nouveau périphérique ajouté au système. Cette fonctionnalité est distincte de la gestion de l'alimentation ; le niveau d'assistance de base doit garantir le bon fonctionnement du système. Le concept de distribution d'énergie permet la construction par blocs (nodales) de nœuds, ce qui permet aux appareils d'interagir avec le système pour atteindre les objectifs énumérés précédemment. Il existe de nombreuses façons d'implémenter la fonctionnalité de gestion de l'alimentation dans un système, et comment elles vont au-delà de la norme.

Les périphériques qui seront présentés sur les cartes d'extension Hot-Plug doivent implémenter des fonctions de distribution d'alimentation. Les appareils conçus pour être utilisés sur des cartes d'extension ou des cartes mères ont la possibilité de prendre en charge la fonction de distribution d'alimentation. Les appareils conçus à la fois pour les cartes d'extension et les modules doivent également mettre en œuvre la distribution de l'alimentation. La norme PCI Express exige que les périphériques et/ou les cartes d'extension dépassent la limite de puissance de « configuration » autorisée telle que définie dans les spécifications électromécaniques applicables avant que le processus de configuration ne soit terminé et activé par le système. Les systèmes doivent distribuer correctement l'alimentation avant de brancher des cartes d'extension.

Alimentation complète du système (informations sur l'alimentation) ;

Pleine puissance allouée par le micrologiciel du système (périphériques de la carte mère) ;

Le nombre total d'emplacements et les types d'emplacements.

Le micrologiciel du système est chargé d'alimenter tous les périphériques de la carte mère qui n'ont pas de fonctions de distribution d'alimentation. Le micrologiciel peut couvrir les périphériques PCI Express standard connectés à des rails d'alimentation standard ou ne pas les alimenter. Lorsque le micrologiciel a alloué de l'alimentation à l'appareil, le logiciel doit définir le bit SYSTEM_ALLOC du registre de capacité du budget d'alimentation (registre de l'appareil) sur un état logique « 1 » pour indiquer le succès de l'opération. Le Power Distribution Manager est responsable de l'allocation de l'alimentation à tous les périphériques PCI Express, y compris les périphériques de carte mère qui ont des fonctions de distribution d'alimentation mais qui ont été marqués pour l'allocation. Le Power Distribution Manager est également chargé de déterminer la connectivité Hot-Plug dans le système.

Ces méthodes peuvent fournir la même fonctionnalité, et le processus de distribution d'énergie n'a pas besoin d'être mis en œuvre de cette manière.

Contrôle de limite de puissance de fente. PCI Express fournit un mécanisme de limitation contrôlée par logiciel de la puissance maximale par emplacement qu'une carte ou un module PCI Express (associé à cet emplacement) peut consommer. Les éléments clés de ce mécanisme sont :

les champs Slot Power Limit Value et Scale du registre Slot Capability mis en œuvre dans les ports en aval du complexe racine et du commutateur ;

les champs Slot Power Limit Value et Scale du registre Device Capability mis en œuvre dans les ports en amont du terminal, du commutateur et du pont PCI Express vers PCI ;

Message Set_Slot_Power_Limit. Ce message transfère le contenu des champs Slot Power Limit Value et Scale du registre Slot Capability du port en aval (complexe racine ou commutateur) vers les champs Slot Power Limit Value et Scale correspondants du registre Device Capability du port en amont. d'un composant attaché au même canal.

Les limites de consommation d'énergie sur une plate-forme sont généralement contrôlées par un logiciel (par exemple, le micrologiciel de la plate-forme), qui est spécifique à la plate-forme, comme :

Séparation de la plate-forme, y compris les emplacements pour l'extension d'E/S à l'aide de cartes/modules d'extension ;

Capacités d'alimentation électrique ;

Capacités de température.

Ce logiciel est responsable de la programmation correcte des champs Slot Power Limit Value et Scale des registres Slot Capability des ports en aval connectés aux slots d'extension. Une fois que la valeur a été écrite dans le registre à l'intérieur du port aval, elle est transférée à un autre composant connecté à ce port par le message "Set_SlotJPower_Limit". Le destinataire doit utiliser la valeur contenue dans le message pour limiter la consommation électrique de l'ensemble de la carte/du module. Les exceptions sont les cartes / modules, qui ne dépassent en aucun cas la valeur minimale spécifiée dans la spécification électromécanique correspondante. Il est supposé que le logiciel du pilote de périphérique de la carte / module sera capable (en lisant le champ Slot Power Limit Value et Scale du registre Device Capability) de configurer le matériel de la carte / du module de sorte que la carte / le module ne dépasse pas la limite dictée. . Dans le cas où la plate-forme définit une limite inférieure au minimum requis pour un fonctionnement normal, le pilote de périphérique doit être en mesure de signaler cet écart au niveau supérieur du logiciel de configuration.

Le système doit respecter les règles suivantes concernant le mécanisme de contrôle "Slot Power Limit". pour les cartes / modules :

Jusqu'à ce qu'un message "Set_Slot_Power_Limit" soit reçu indiquant une valeur limite supérieure au minimum spécifié dans la spécification électromécanique pour le facteur de forme de la carte ou du module, la carte/le module ne doit pas consommer plus de puissance que celle spécifiée par cette valeur minimale ;

La consommation électrique maximale autorisée pour la carte / le module est déterminée par la valeur la plus élevée de tous les messages "Set_Slot_Power_Lim it" reçus.

Il est interdit aux points de terminaison, commutateur et pont PCI Express-to-PC 1 d'être regroupés sur une carte/un module où la consommation électrique totale est inférieure à la limite minimale pour le facteur de forme donné d'ignorer les messages "Set_Slot_Powcr_Limit" et de renvoyer la valeur " 0 "dans la valeur limite de puissance de l'emplacement et les zéros d'échelle du registre de capacité du périphérique.

Les composants répertoriés ci-dessus doivent accepter correctement le message "Set_Slot_Power_Limit", mais au lieu de le traiter, supprimez-le simplement.

Règles relatives au mécanisme de contrôle « Slot Power Limit » pour les complexes racine et les commutateurs contenant des emplacements :

Le port aval ne doit pas transmettre le message "Set_Slot_Power_Limit", dont la limite sera inférieure à la valeur minimale spécifiée dans la spécification électromécanique pour le facteur de forme de ces slots.

Registres de contrôleFentePouvoirLimite. En règle générale, les registres de limite de puissance des emplacements à l'intérieur des ports en aval du complexe racine ou du commutateur sont programmés avec un logiciel spécifique à la plate-forme. Certaines implémentations peuvent utiliser la méthode matérielle pour initialiser la valeur de ces registres et ne nécessitent donc pas de support logiciel.

Les terminaux, commutateurs et ponts PCT Express vers PCI conçus pour l'agrégation de cartes/modules où la consommation électrique totale est inférieure au minimum spécifié pour le facteur de forme peuvent ignorer les messages Set_Slot_Power_Limit. Les composants PCI Express implémentés de cette manière peuvent ne pas être compatibles avec les futurs facteurs de forme potentiels. De tels facteurs de forme indiqueront peut-être une limite de consommation d'énergie inférieure au minimum requis pour une nouvelle carte / module conçu avec des composants existants.

introduction

La loi de Moore stipule que le nombre de transistors sur une puce de silicium qu'il est rentable de fabriquer double tous les deux ans. Mais ne pensez pas que la vitesse du processeur double également tous les deux ans. Il s'agit d'une idée fausse courante parmi beaucoup, et les utilisateurs s'attendent souvent à ce que les performances du PC évoluent de manière exponentielle.

Cependant, comme vous l'avez peut-être remarqué, les meilleurs processeurs du marché sont bloqués entre 3 et 4 GHz depuis maintenant six ans. Et l'industrie informatique a dû trouver de nouvelles façons d'augmenter les performances informatiques. La plus importante de ces méthodes est de maintenir un équilibre entre les composants de la plate-forme qui utilisent le bus PCI Express, une norme ouverte qui permet aux cartes graphiques haute vitesse, aux cartes d'extension et à d'autres composants d'échanger des informations. Et PCI Express est tout aussi important pour l'évolutivité des performances que les processeurs multicœurs. Alors que les processeurs dual-core, quad-core et six-core ne peuvent être chargés qu'avec des applications optimisées pour le multithreading, tout programme installé sur votre ordinateur interagit d'une manière ou d'une autre avec les composants connectés via PCI Express.

De nombreux journalistes et experts s'attendaient à ce que les cartes mères et chipsets PCI Express 3.0 de nouvelle génération apparaissent au premier trimestre 2010. Malheureusement, des problèmes de compatibilité descendante ont retardé PCI Express 3.0, et aujourd'hui cela fait six mois, mais nous attendons toujours les informations officielles sur le publication de la nouvelle norme.

Cependant, nous avons discuté avec le PCI-SIG (Groupe d'Intérêt Spécial, qui est responsable du PCI et du PCI Express), ce qui nous a permis d'obtenir quelques réponses.

PCI Express 3.0 : forfaits

Al Yanes, président et président de PCI-SIG, et Ramin Neshati, président du groupe de travail sur les communications série PCI-SIG, ont partagé leurs plans actuels pour PCI Express 3.0.

|

Cliquez sur l'image pour agrandir.

Le 23 juin 2010, la version 0.71 de la spécification PCI Express 3.0 a été publiée. Yans a fait valoir que la version 0.71 devrait résoudre tous les problèmes de compatibilité descendante qui ont causé le retard initial. Neshati a noté que le principal problème de compatibilité était la fonctionnalité "DC errant", qu'il a expliquée comme PCI Express 2.0 et les périphériques antérieurs "ne donnaient pas les zéros et les uns nécessaires" pour correspondre à l'interface PCI Express 3.0.

Aujourd'hui, les problèmes de compatibilité descendante étant résolus, PCI-SIG est sur le point de publier la version de base 0.9 "plus tard cet été". Et derrière cette version de base, la version 1.0 est attendue au quatrième trimestre de cette année.

Bien sûr, la question la plus intrigante est de savoir quand les cartes mères PCI Express 3.0 arriveront-elles dans les magasins. Neshati a noté qu'il s'attend à ce que les premiers produits apparaissent au premier trimestre de 2011 (triangle "Pour info" sur la photo avec le plan).

Neshati a ajouté qu'il ne devrait y avoir aucun changement au niveau du silicium entre les versions 0.9 et 1.0 (c'est-à-dire que tous les changements n'affecteront que les logiciels et micrologiciels), donc certains produits devraient être commercialisés avant même que la spécification 1.0 finale n'apparaisse. Et les produits peuvent déjà être certifiés pour la "liste d'intégrateurs" PCI-SIG (triangle "IL"), qui est une variante du logo de conformité PCI-SIG.

Neshati a nommé en plaisantant le troisième trimestre de 2011 comme la date « Fry's and Buy » (probablement en référence à Frys.com, Buy.com ou Best Buy). C'est-à-dire qu'au cours de cette période, nous devrions nous attendre à l'apparition d'un grand nombre de produits prenant en charge PCI Express 3.0 dans les magasins de détail et les magasins en ligne.

PCI Express 3.0 : conçu pour la vitesse

Pour les utilisateurs finaux, la principale différence entre PCI Express 2.0 et PCI Express 3.0 sera une augmentation significative de la bande passante maximale. PCI Express 2.0 a un taux de transmission du signal de 5 GT/s, c'est-à-dire que le débit est de 500 Mo/s pour chaque ligne. Ainsi, le slot graphique PCI Express 2.0 principal, qui utilise typiquement 16 voies, fournit une bande passante bidirectionnelle jusqu'à 8 Go/s.

Avec PCI Express 3.0, nous obtiendrons un doublement de ces indicateurs. Le PCI Express 3.0 utilise un débit de signalisation de 8 GT/s, ce qui donne 1 Go/s de bande passante par voie. Ainsi, le slot principal pour la carte vidéo recevra une bande passante allant jusqu'à 16 Go / s.

À première vue, l'augmentation de la vitesse du signal de 5 GT/s à 8 GT/s ne semble pas être un doublement. Cependant, la norme PCI Express 2.0 utilise un schéma de codage 8b/10b, où 8 bits de données sont transmis sous forme de caractères 10 bits pour la récupération d'erreurs. En conséquence, nous obtenons une redondance de 20%, c'est-à-dire une diminution de la bande passante utilisable.

PCI Express 3.0 passe à un schéma de codage 128b/130b beaucoup plus efficace, éliminant ainsi 20 % de redondance. Par conséquent, 8 GT/s n'est plus une vitesse « théorique » ; c'est le débit réel, comparable en performances au débit du signal de 10 GT/s si le principe de codage 8b/10b était utilisé.

|

Cliquez sur l'image pour agrandir.

Nous avons interrogé Yans sur les appareils qui nécessiteraient une augmentation de la vitesse. Il a répondu que ceux-ci incluront "des commutateurs PLX, des contrôleurs Ethernet 40 Gbps, InfiniBand, des périphériques à semi-conducteurs qui deviennent de plus en plus populaires et, bien sûr, des cartes graphiques". Il a ajouté "Nous n'avons pas manqué d'innovations, elles n'apparaissent pas de manière statique, elles sont un flux continu", elles ouvrent la voie à de nouvelles améliorations dans les futures versions de l'interface PCI Express.

Analyse : où utiliserons-nous PCI Express 3.0 ?

Périphériques de stockage

AMD a déjà intégré le support SATA 6Gb/s dans sa 8ème gamme de chipsets, et les fabricants de cartes mères ajoutent des contrôleurs USB 3.0. Intel est un peu à la traîne dans ce domaine, puisqu'il ne prend pas en charge l'USB 3.0 ou le SATA 6 Gb/s dans les chipsets (nous avons déjà des échantillons préliminaires de cartes mères sur la P67 dans notre laboratoire, et elles prennent en charge le SATA 6 Gb/s, mais USB 3.0 dans cette génération, nous ne recevrons pas). Cependant, comme nous l'avons vu à plusieurs reprises dans la confrontation entre AMD et Intel, les innovations AMD inspirent souvent Intel. Compte tenu de la vitesse de l'interface de stockage et des périphériques de nouvelle génération, il n'est pas encore nécessaire de porter les technologies sur PCI Express 3.0. Tant pour l'USB 3.0 (5 Gb/s) que pour le SATA 6 Gb/s (il n'y a pas encore de disques qui viendraient aux limites de cette interface), une seule ligne PCI Express de deuxième génération suffira.

Bien sûr, en ce qui concerne les lecteurs, l'interaction entre les lecteurs et les contrôleurs n'est qu'une partie de la question. Imaginez un ensemble de plusieurs SSD avec Interface SATA 6 Gbps pour le chipset lorsque matrice RAID 0 a le potentiel de charger une voie PCI Express Gen 2 que la plupart des fabricants de cartes mères utilisent pour brancher un contrôleur. Ainsi, après quelques calculs simples, vous pouvez décider si les interfaces USB 3.0 et SATA 6 Gb/s peuvent vraiment nécessiter la prise en charge de PCI Express 3.0.

|

Cliquez sur l'image pour agrandir.

Comme nous l'avons déjà mentionné, l'interface USB 3.0 offre une vitesse maximale de 5 Gbps. Mais en tant que norme PCI Express 2.1, l'USB 3.0 utilise un codage 8b/10b, ce qui signifie que la vitesse de pointe réelle est de 4 Gbit/s. Divisez les bits par huit pour convertir en octets, et vous obtenez un débit maximal de 500 Mo / s - exactement le même qu'une seule voie dans la norme PCI Express 2.1 actuelle. Le SATA 6 Gb/s fonctionne à 6 Gb/s, mais il utilise également un schéma de codage 8b/10b, qui traduit les 6 Gb/s théoriques en 4,8 Gb/s réels. Encore une fois, convertissez cette valeur en octets et vous obtenez 600 Mo/s, soit 20% de plus que ce que la ligne PCI Express 2.0 peut fournir.

Cependant, le problème réside dans le fait que même les SSD les plus rapides d'aujourd'hui ne peuvent pas charger complètement une connexion SATA 3Gb/s. Les périphériques ne s'approchent pas de la charge de l'interface USB 3.0, il en va de même pour la dernière génération de SATA 6Gb/s. Au moins aujourd'hui, PCI Express 3.0 n'est pas nécessaire à sa promotion active sur le marché des plateformes. Mais espérons qu'à mesure qu'Intel passe à la production Flash NAND troisième génération, les vitesses d'horloge augmenteront et nous aurons des appareils capables de dépasser le niveau 3Gb / s des ports SATA de deuxième génération.

Cartes vidéo

Nous avons mené nos propres recherches sur l'impact de la bande passante PCI Express sur les performances des cartes vidéo - PCI Express 2.0 post-commercialisation , début 2010 et aussi récemment... Nous avons eu beaucoup de mal à charger la bande passante x16 actuellement disponible sur les cartes mères PCI Express 2.1. Vous aurez besoin d'une configuration multi-GPU ou d'une carte graphique extrêmement haut de gamme sur un seul GPU pour faire la différence entre les connexions x8 et x16.

Nous avons demandé à AMD et Nvidia de commenter le besoin de PCI Express 3.0 - ce bus rapide sera-t-il nécessaire pour libérer le plein potentiel de performances des cartes graphiques de prochaine génération ? Un porte-parole d'AMD nous a dit qu'il ne pouvait pas encore commenter.

|

Cliquez sur l'image pour agrandir.

Un porte-parole de Nvidia s'est montré plus accommodant : "Nvidia a joué un rôle clé dans l'industrie dans le développement de PCI Express 3.0, qui devrait doubler la bande passante de la norme de génération actuelle (2.0). Les consommateurs et les professionnels bénéficieront de la nouvelle norme avec des graphiques et des calculs améliorés. performances dans les ordinateurs portables, les ordinateurs de bureau, les postes de travail et les serveurs avec GPU. "

Peut-être que la phrase clé peut être appelée "il y aura des applications qui pourront les utiliser". On dirait que rien ne devient plus petit dans le monde graphique. Les écrans s'agrandissent une haute résolution remplace la définition standard, les textures dans les jeux deviennent de plus en plus détaillées et intrigantes. Aujourd'hui, nous ne pensons pas que même les dernières cartes graphiques haut de gamme aient besoin d'une interface PCI Express 3.0 à 16 voies. Mais les passionnés ont vu l'histoire se répéter année après année : les progrès technologiques ouvrent la voie à de nouvelles façons d'utiliser des « tuyaux plus épais ». Nous assisterons peut-être à une croissance explosive des applications qui rendront le GPU computing plus courant. Ou, peut-être, une baisse des performances observée lors d'un manque de mémoire de la carte vidéo, lors du passage de mémoire système ne sera plus aussi perceptible dans les produits de masse et bas de gamme. En tout cas, nous sommes sur le point de voir les innovations que le PCI Express 3.0 apportera à AMD et Nvidia.

Connexions des composants de la carte mère

AMD et Intel sont toujours très réticents à partager des informations sur les interfaces qu'ils utilisent pour communiquer entre les composants du chipset ou les "blocs de construction" logiques dans les ponts nord/sud. On sait à quelle vitesse ces interfaces fonctionnent, et aussi qu'elles sont conçues pour ne pas créer de goulots d'étranglement si possible. Parfois, nous savons qui a produit une certaine partie logique du système par exemple, AMD a utilisé un contrôleur SATA basé sur Silicon Logic dans le SB600. Mais la technologie utilisée pour construire des ponts entre les composants reste souvent des « points blancs ». PCI Express 3.0, bien sûr, semble être une solution très attrayante, à l'instar de l'interface A-Link utilisée par AMD.

L'apparition récente de contrôleurs USB 3.0 et SATA 6 Gb/s sur un grand nombre de cartes mères permet également de faire le point. Étant donné que le chipset Intel X58 ne fournit de support natif pour aucune des deux technologies, des entreprises telles que Gigabyte doivent intégrer des contrôleurs sur leurs cartes mères en utilisant les voies disponibles pour les connecter.

La carte mère Gigabyte EX58-UD5 ne supporte ni l'USB 3.0 ni le SATA 6Gb/s. Cependant, il dispose d'un slot PCI Express x4.

|

Cliquez sur l'image pour agrandir.

Gigabyte remplace la carte mère EX58-UD5 nouveau modèle X58A-UD5, qui prend en charge deux ports USB 3.0 et deux ports SATA 6 Gb/s. Où Gigabyte a-t-il trouvé la bande passante pour prendre en charge ces deux technologies ? La société a pris le PCI Express 2.0 sous une ligne pour chaque contrôleur, réduisant les possibilités d'installation de cartes d'extension, mais enrichissant en même temps les fonctionnalités de la carte mère.

Hormis l'ajout de l'USB 3.0 et du SATA 6Gb/s, la seule différence notable entre les deux cartes mères concerne la suppression du slot x4.

|

Cliquez sur l'image pour agrandir.

L'interface PCI Express 3.0, comme les standards avant elle, permettra-t-elle d'ajouter de futures technologies et contrôleurs aux cartes mères qui ne seront pas présentes dans les générations actuelles de chipsets sous une forme intégrée ? Il nous semble qu'il en sera ainsi.

CUDA et calcul parallèle

Nous entrons dans l'ère des supercalculateurs de bureau. Nos systèmes sont alimentés par des GPU intensifs en parallèle, des alimentations et des cartes mères capables de prendre en charge jusqu'à quatre cartes vidéo simultanément. Technologie Nvidia CUDA vous permet de convertir une carte vidéo en un outil pour les programmeurs pour les calculs non seulement dans les jeux, mais aussi dans les domaines scientifiques, et dans applications d'ingénierie... L'interface de programmation a déjà fait ses preuves lors de développer une variété de solutions pour le secteur des entreprises y compris l'imagerie médicale, les mathématiques, l'exploration pétrolière et gazière.

|

Cliquez sur l'image pour agrandir.

Nous avons demandé l'avis du programmeur OpenGL Terry Welsh de Économiseurs d'écran vraiment élégantsà propos de PCI Express 3.0 et de l'informatique GPU. Terry nous a dit que "PCI Express a pris une bonne longueur d'avance et j'aime que les développeurs doublent la bande passante quand ils le souhaitent - comme avec la version 3.0. Cependant, dans les projets sur lesquels je dois travailler, je ne m'attends pas à voir de différence Mon travail est lié aux simulateurs de vol, mais ils ont tendance à être limités par la mémoire et les performances d'E/S du disque dur ; le bus graphique n'est pas du tout un goulot d'étranglement. Le GPU computing, pour les personnes faisant du travail scientifique avec du big data.

|

Cliquez sur l'image pour agrandir.