Microcircuits numériques. Types de logique, boîtiers

Eh bien, disons d'abord ceci: les microcircuits sont divisés en deux grands types: analogiques et numériques. Les circuits intégrés analogiques fonctionnent avec Signal analogique, et numérique, respectivement - avec numérique. Nous parlerons plus précisément des microcircuits numériques.

Plus précisément, même, nous ne parlerons pas de microcircuits, mais d'éléments de technologie numérique qui peuvent être "cachés" à l'intérieur du microcircuit.

Quels sont ces éléments ?

Certains des noms que vous avez entendus, d'autres, peut-être pas. Mais croyez-moi, ces noms peuvent être prononcés à haute voix dans n'importe quelle société culturelle - ce sont des mots absolument décents. Donc, une liste approximative de ce que nous allons étudier:

- Déclencheurs

- Compteurs

- Brouilleurs

- Décodeurs

- Multiplexeurs

- Comparateurs

Tous les microcircuits numériques fonctionnent avec signaux numériques... Ce que c'est?

Signaux numériques- ce sont des signaux qui ont deux niveaux stables - un niveau logique zéro et un niveau logique un. Dans les microcircuits réalisés à l'aide de diverses technologies, niveaux logiques peuvent différer les uns des autres.

Actuellement, deux technologies sont les plus utilisées : le TTL et le CMOS.

TTL- Logique transistor-transistor ;

CMOS- Métal-Oxyde-Semiconducteur gratuit.

Pour TTL, le niveau zéro est de 0,4 V, le niveau unitaire est de 2,4 V.

Pour la logique CMOS, le niveau zéro est très proche de zéro volt, le niveau un est approximativement égal à la tension d'alimentation.

Dans tous les sens, un - lorsque la tension est élevée, zéro - lorsqu'elle est faible.

MAIS! Une tension nulle à la sortie du microcircuit ne signifie pas que la sortie "pend dans l'air". En fait, il est juste relié à la terre. Par conséquent, plusieurs conclusions logiques ne peuvent pas être connectées directement : s'il y a différents niveaux sur eux, un court-circuit se produira.

En plus des différences de niveaux de signal, les types de logique diffèrent également par la consommation électrique, la vitesse (limite de fréquence), la capacité de charge, etc.

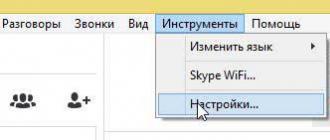

Le type de logique peut être reconnu par le nom du microcircuit. Plus précisément - par les premières lettres du nom, qui indiquent à quelle série appartient le microcircuit. Au sein de n'importe quelle série, il peut y avoir des microcircuits réalisés en utilisant une seule technologie. Pour vous faciliter la navigation, voici un petit tableau croisé dynamique :

| TTL | TTLSh | CMOS | Bastrode. CMOS | ALS | |

| Explication du nom | Logique transistor-transistor | TTL avec diode Schottky | Semi-conducteur à oxyde métallique gratuit | Logique cohérente avec l'émetteur | |

| Série de base d'odech. microcircuits | K155 K131 |

K555 K531 KR1533 |

K561 K176 |

KR1554 KR1564 |

K500 KR1500 |

| Série de microcircuits bourgeois | 74 | 74LS 74ALS |

CD40 H 4000 |

74AC 74 CH |

MC10 F100 |

| Délai de propagation, nS | 10…30 | 4…20 | 15…50 | 3,5..5 | 0,5…2 |

| Max. fréquence, MHz | 15 | 50..70 | 1…5 | 50…150 | 300…500 |

| Tension d'alimentation, V | 5 ± 0,5 | 5 ± 0,5 | 3...15 | 2...6 | -5,2 ± 0,5 |

| Courant de consommation (sans charge), mA | 20 | 4...40 | 0,002...0,1 | 0,002...0,1 | 0,4 |

| Niveau de journal 0, V | 0,4 | 0,5 | < 0,1 | < 0,1 | -1,65 |

| Niveau de journal. 1, B | 2,4 | 2,7 | ~ U fosse | ~ U fosse | -0,96 |

| Max. courant de sortie, mA | 16 | 20 | 0,5 | 75 | 40 |

Les plus courantes aujourd'hui sont les séries suivantes (et leurs homologues importées) :

- TTLSh - K555, K1533

- CMOS - KR561, KR1554, KR1564

- ESL - K1500

Le type de logique est choisi principalement en fonction des considérations suivantes :

Vitesse (fréquence de fonctionnement)

- consommation d'énergie

- le prix

Mais il y a des situations où un type ne peut pas suffire. Par exemple, une unité doit être à faible puissance et l'autre à grande vitesse. Les puces de technologie CMOS ont une faible consommation. Haute vitesse - à ESL.

Dans ce cas, vous devrez installer des convertisseurs de niveau.

Certes, certains types peuvent être bien appariés sans convertisseurs. Par exemple, un signal de la sortie d'un microcircuit CMOS peut être appliqué à l'entrée d'un micro Schémas TTL(étant donné que leurs tensions d'alimentation sont les mêmes). Cependant, dans verso, c'est-à-dire qu'il n'est pas recommandé d'exécuter un signal de TTL vers CMOS.

Les microcircuits sont disponibles dans divers emballages. Le plus commun les types suivants immeubles:

TREMPER

(Pack double en ligne)

Le "cafard" habituel. Nous poussons les pieds dans les trous de la planche - et nous les scellons.

Les jambes dans le corps peuvent être 8, 14, 16, 20, 24, 28, 32, 40, 48 ou 56.

La distance entre les fils (pas) est de 2,5 mm (norme domestique) ou de 2,54 mm (pour la bourgeoisie).

Largeur de plomb environ 0,5 mm

La numérotation des broches est indiquée sur la figure (vue de dessus). Pour déterminer l'emplacement de la première jambe, vous devez trouver la "clé" sur le corps.

SOIC

(Circuit Intégral Petit Contour)

Microcircuit planaire - c'est-à-dire que les pattes sont soudées du même côté de la carte où se trouve le boîtier. En même temps, le microcircuit repose avec son ventre sur la carte.

Le nombre de pattes et leur numérotation sont les mêmes que pour le DIP.

Le pas des conclusions est de 1,25 mm (domestique) ou 1,27 mm (bourgeois).

Largeur de fil - 0,33 ... 0,51

PLCC

(Porte-puce à plomb en J en plastique)

Corps carré (rarement rectangulaire). Les jambes sont situées sur les quatre côtés et ont une forme en J (les extrémités des jambes sont pliées sous l'abdomen).

Les microcircuits sont soit soudés directement sur la carte (planaire), soit insérés dans la prise. Ce dernier est préférable.

Le nombre de pattes est de 20, 28, 32, 44, 52, 68, 84.

Pas des jambes - 1,27 mm

Largeur de fil - 0,66 ... 0,82

Numérotation des broches - la première jambe près de la clé, en augmentant le nombre dans le sens inverse des aiguilles d'une montre :

|

Comment aimez-vous cet article? |

Les microcircuits intégrés de logique transistor-transistor sont des microensembles de faible degré d'intégration, construits sur des transistors bipolaires. Leur principal inconvénient est une faible quantité par cristal, ainsi que la criticité de la tension d'alimentation et un courant de consommation suffisamment important.

Le schéma juste au-dessus montre une porte logique simple - 3I - PAS... Il est basé sur un transistor multi-émetteur bipolaire classique VT1. Le niveau zéro logique à sa sortie apparaîtra en cas de niveaux élevés sur les trois émetteurs en même temps. VT2 prend en charge la fonction d'inversion (NOT gate), et le multi-émetteur VT1 est une porte logique 3I.

Malgré les inconvénients énumérés, la série TTL la plus populaire, K155 est très populaire aujourd'hui, regardez combien de mannequins radio vous pouvez collecter.

La série K155 est la plus grande série TTL. Il contient plus de 100 micro-assemblages qui exécutent diverses fonctions et opérations logiques (ET, OU, NON, ET - NON, OU - NON, déclencheurs, registres, compteurs, additionneurs.

Le niveau d'une unité logique dans les microcircuits de cette série TTL se situe dans la plage de tension de 2,4 V à 5 V), et le niveau d'un zéro logique ne dépasse pas 0,4 V.

Presque tous les micro-assemblages de cette série sont disponibles dans un boîtier standard à 14 broches. Avec un point ou une encoche marquant la première broche. La 7ème broche est le cas ou moins. 14 couché en face du premier est un plus.

La prochaine étape dans l'évolution du K155 était la série K555, dans laquelle le principe de base TTL a été préservé, mais ajouté aux jonctions de collecteur des transistors. Par conséquent, la série K555 s'appelait TTLSh (diode TTL et Schottky). En TTLSh, la consommation d'énergie a diminué d'environ 2 fois et la vitesse a considérablement augmenté.

CI CMOS |

La lettre K au début de l'abréviation signifie - complémentaire... En pratique, cela suggère que des paires avec les mêmes paramètres sont utilisées dans le micro-assemblage, mais un transistor a une grille de type n, et l'autre, respectivement, de type p. Ils sont également appelés CMOS (Complementary Metal-Oxide Semiconductor).

La figure montre un exemple de porte logique de base classique NON. C'est-à-dire que si l'on arrive à l'entrée, la sortie sera déjà un zéro logique et vice versa.

Élément 2I - PAS... À partir de quelques-uns de ces éléments logiques, il est facile d'obtenir et de plusieurs déclencheurs - un compteur, un registre et des dispositifs de mémoire élémentaires.

Et maintenant, une mouche dans la pommade : à la fréquence de fonctionnement maximale, les éléments CMOS sont sensiblement inférieurs aux autres logiques sur les transistors bipolaires (TTL) et ils sont souvent sensibles à l'électricité statique.

Microcircuits basés sur des structures CMDP

Les circuits intégrés numériques basés sur des structures CMDP sont de plus en plus utilisés dans le développement de divers circuits électroniques, pour de très bonnes raisons. KMDP IMS est un appareil très polyvalent et facile à utiliser qui possède des propriétés uniques qui ne sont pas typiques des autres classes d'IMS numériques.

Ces circuits intégrés sont dits complémentaires car ils sont réalisés à base de transistors CMDP, c'est-à-dire basé sur des paires transistors à effet de champ avec la structure : métal - oxyde (diélectrique) - semi-conducteur, ayant des caractéristiques et des canaux très similaires différents types conductivité. Les circuits intégrés construits sur ce principe consomment beaucoup moins d'énergie de la source d'alimentation que tous les autres circuits intégrés et peuvent fonctionner dans une plus large gamme de niveaux de tension d'alimentation. Électronique Montre-bracelet et appareils automobiles, appareils électroniques médicaux, récepteurs de télévision, calculatrices portables - ce ne sont là que quelques exemples d'appareils dans lesquels CMDP IMS est utilisé.

Les principaux avantages des circuits intégrés numériques basés sur des structures CMOS sont une grande impédance d'entrée des transistors (R in) 10 12 Ohm) et haut niveau l'intégration. Tout en faisant dispositifs d'impulsion sur intégrale des portes logiques En raison des résistances d'entrée élevées des transistors, les résistances CMOS des résistances de synchronisation ne sont pas limitées par le haut. Par conséquent, pour obtenir des impulsions de longue durée, la capacité électrique des condensateurs de synchronisation ne doit pas être augmentée.

Les structures complémentaires sont des paires complémentaires de transistors bipolaires (p-n-p et n-p-n) ou MIS (canal p et canal n), qui peuvent améliorer considérablement les caractéristiques du circuit intégré. Ils sont réalisés sur un support commun dans des poches isolées du support ou p-n-jonction, ou un film diélectrique. Les transistors complémentaires sont réalisés sous la forme de structures horizontales et verticales.

Dans les transistors à structure horizontale, l'émetteur, la base et le collecteur sont situés sur le même plan horizontal, de sorte que les porteurs minoritaires injectés dans la base ne se déplacent pas perpendiculairement à la surface du cristal, mais le long de celle-ci. De tels transistors sont appelés fin (latéral). Dans la fabrication de fin

Transistors p-n-p - la formation d'émetteurs est réalisée lors de la diffusion de base des transistors n-p-n -. Ensuite, à travers la seconde diffusion de base, l'émetteur du transistor pnp est entouré d'un collecteur. La base du transistor est la couche semi-conductrice de type n d'origine entre ces régions. La largeur de la base, donc, et la valeur du coefficient de transfert de courant de la base et sont déterminées par la distance entre les fenêtres gravées en mode photo pour l'émetteur et le collecteur.

Dans les structures verticales, la base est située sous l'émetteur (les porteurs minoritaires injectés se déplacent dans une direction perpendiculaire à la surface du cristal). Tous les trois zones pnp- les transistors (collecteur, base et émetteur) sont formés par diffusion. De telles structures complémentaires sont difficiles à fabriquer en raison des exigences de haute précision pour la concentration des dopants. Cependant, les transistors fabriqués selon cette technologie ont un coefficient de transfert de courant de base plus élevé que les transistors à structure horizontale et une tension de claquage élevée de la jonction collecteur.

La base des éléments CMOS est un inverseur construit sur deux transistors MOS complémentaires (complémentaires) ( m-MOS et p-MOS) avec une grille isolée et un canal induit. Une caractéristique de ce schéma ( riz. 4.17) est que la tension d'entrée contrôle non seulement la clé, mais aussi le transistor de charge.

Sur le riz. 4.5.2. les caractéristiques drain-grille des transistors utilisés sont données. Transistor avec m-canal ( VT n) commence à conduire le courant si une tension positive est appliquée à sa grille, et un transistor avec R-canal ( Vermont p) - si une tension négative est appliquée à sa grille par rapport à la source.

Il est important que les deux transistors aient un talon sur leurs caractéristiques drain-grille. Ainsi, si l'on veut que le circuit fonctionne avec une tension d'alimentation positive (+ E P), alors comme transistor clé il faut utiliser VT n, et comme charge - VT p.

Riz. 4.17.1. Onduleur CMOS

Riz. 4.5.2. Caractéristiques drain-grille des transistors CMOS

Onduleur ( riz. 4.17) est construit de telle sorte que la source Vermont p est connecté à Fr, et la source VT n- avec le sol. Fermetures VT n et Vermont p sont combinés et servent d'entrée de l'onduleur, les drains VT n et Vermont p sont également combinés et servent de sortie de l'onduleur. Avec cette inclusion, les formules suivantes pour déterminer la tension grille-source seront valides VT n et Vermont p : U zip = U in, U zir = U in -E p

U zip- tension grille-source m-transistor à canal ( VT n);

U zir- tension grille-source R-transistor à canal ( VT p).

Lors de l'examen du fonctionnement de l'onduleur, nous supposerons que VT n et Vermont p ont des caractéristiques identiques et la tension de seuil U =½ U Pr½ = 1,5V.

Jusqu'à pp- tension de seuil m-transistor à canal ;

U Pr- tension de seuil p-transistor à canal.

Considérons le fonctionnement d'un onduleur CMOS selon sa HVV ( riz. 4.18-a), sur lesquelles on peut distinguer quatre sections et dépendances U ZI = F(U-BX) (riz. 4.18-b).

Section 1: U 0 en £ U Пп... Où U zip = U dans et VT n fermé, U zir = U in - E p< U Pr et VT p ouvert.

Riz. 4.18. Spécifications de l'onduleur CMOS :

a) HVB, b) U OBTURATEUR-SOURCE = f (U IN); c) I PTR = f (U BX)

VT n fermé), Vermont p est en saturation profonde, et la sortie aura une tension proche de E N.-É. ( U 1 SORTIE » E NS).

Section II : U P> U IN> U Pp,

où EN HAUT - tension de commutation

et U OUT = 0,5 (U 1 - U 0). U SPTA = U IN> U Pp et VT n commence à s'ouvrir, U ЗИР = U -Е П< U Пр et Vermont p est ouvert.

Sur ce site ½ U SPTA½ < ½ U ZIR½, donc Vermont p restera saturé et VT n- en mode actif.

VT n.

Le courant circulant dans le circuit crée une chute de tension à travers le canal Vermont p, à cause de cela, la tension de sortie commence à diminuer. Cependant, avec une augmentation de la tension d'entrée dans cette section, la tension de sortie diminue légèrement, car Vermont p est toujours saturé.

Point En haut:U IN = U P = 0,5E P;

U SPTA = U IN = U P> U Pp, et VT n ouvert; 0.5E P< U Пр et Vermont p est ouvert.

À ce stade | U SPTA|=|U ZIR| par conséquent, les résistances des canaux des deux transistors sont également égales. Ainsi, la sortie sera une tension égale à la moitié de la tension de l'alimentation ( U OUT=0,5E NS). Ce point correspond à la section verticale sur la caractéristique. À ce stade, le circuit consomme un courant maximal, car les deux transistors sont activés. Au moindre changement de la tension d'entrée, la tension de sortie change radicalement.

Section III : E P -½ U Pr½ > U IN> U P;U SPTA= U ВХ> U Пп et VT n ouvert; U ЗИР = U -Е П< U Пр et Vermont P est ouvert, mais avec croissance U-BX devient de moins en moins ouvert.

Sur ce site U SPTA>|U ZIR|, et donc VT n est en saturation, un Vermont p - en mode actif.

Le courant consommé par le circuit est déterminé dans ce cas par le transistor Vermont p.

La tension de sortie dans cette section est égale à la chute de tension sur le canal VT n... Comme VT n est en saturation, alors cette chute est faible, et avec une augmentation U-BX il diminue de plus en plus.

Section IV : E p> U in> E p -½ U Pr½; U zip= U dans> U Pp et Vn ouvert; U zir = U dans -E n> U zip et Vermont p est fermé.

Dans cet état, le circuit ne consomme pratiquement pas de courant (puisque Vermont p est fermé). VT n est en saturation profonde, tandis que la sortie aura une tension proche de zéro ( Tu es dehors» 0).

Comme le montre le HVB ( riz 4.5.1а), les éléments CMOS ont une bonne immunité au bruit. L'immunité au bruit est égale à zéro et un. En effet, le point de commutation ( U dans = U P) se situe exactement au centre de la plage de tension d'entrée ( E P> U dans> 0). À E P= + 5V valeur maximum les interférences peuvent atteindre 1,5 V. Avec la croissance E P l'immunité absolue au bruit est augmentée. L'immunité des éléments CMOS est d'environ 30% de E P (U 0 au maximum"0.3 E P, U 1 po.min"0.7 E P).

Étant donné que l'entrée de l'inverseur CMOS est constituée de MOSFET à grille isolée, l'impédance d'entrée est très élevée (10 12 10 13 Ohm). Par conséquent, de tels circuits ne consomment pratiquement pas de courant à l'entrée.

L'impédance de sortie des circuits CMOS est petite comme dans l'état Log. 0 et à l'état Log. 1, puisque l'un des transistors VT n ou alors Vermont p sera certainement ouvert. Ainsi, la résistance de sortie est déterminée par la résistance de canal du transistor MOS ouvert et est de 10 2 10 3 Ohm.

Une impédance d'entrée élevée et une impédance de sortie faible entraînent un rapport de dérivation statique élevé à la sortie. Le facteur de branchement sera limité par le haut uniquement par les exigences de vitesse. Étant donné que chaque entrée du circuit a une certaine capacité, alors avec une augmentation du facteur de dérivation, la capacité de charge augmentera, ce qui, à son tour, augmentera le temps de commutation de l'élément.

Ainsi, à mesure que la fréquence de fonctionnement diminue, le rapport de branchement augmentera. En relation avec ce qui précède, il est clair que les caractéristiques d'entrée et de charge perdent leur signification. La caractéristique de charge n'est importante que lors du couplage d'éléments CMOS avec des éléments d'autres types.

La faible impédance de sortie de l'élément dans les deux états permet de recharger rapidement la capacité de charge. Il en résulte des délais d'activation et de désactivation rapides. En pratique, les temps de retard sont de 50 200 ns.

Riz. 4.5.1c explique le processus de consommation de courant par le circuit.

En position statique, les circuits CMOS consomment très peu de courant (10 -6 -10 -7 A).

Fondamentalement, le courant est consommé lors de la commutation d'un circuit, tandis que U SPTA et ½ U ZIR½> U POR et les deux transistors VT n et VT p ouvert (sections II et III sur CVB) Cependant, la valeur de ce courant est inférieure à celle des circuits TTL, car les résistances volumiques des transistors MOS ouverts dépassent les résistances des transistors bipolaires ouverts. Pour cette raison, il n'y a pas de résistance d'écrêtage dans les circuits CMOS.

Lors de la commutation du circuit, le courant est également consommé pour charger la capacité de charge. L'amplitude de ce courant peut être définie comme I = CEf П où fP Est la fréquence de commutation du circuit.

Les avantages des circuits CMOS incluent également la possibilité de fonctionner à différentes tensions d'alimentation (3-15V). Avec une augmentation de la tension d'alimentation, l'immunité absolue au bruit augmentera, mais la consommation de courant augmentera également (les sections II et III sur le CVB deviendront plus larges). Avec une tension d'alimentation de + 5V, les niveaux de signaux des circuits CMOS deviennent compatibles avec les niveaux de TTL. Dans ce cas, cependant, il faut veiller à U 1 I/min pour le CMOS serait plus E N.-É. - |U OL | pour un verrouillage sécurisé VT p... A cet effet, la sortie TTL est souvent connectée via une résistance à E P.

Le travail des circuits CMOS sur les circuits TTL est généralement effectué à l'aide de schémas de câblage.

Sur le riz. 4.19 le schéma de l'élément de base de type CMOS est représenté. L'élément implémente la fonction 4I-NOT. Les transistors sont positionnés de manière à ce qu'aucun courant traversant ne circule dans le circuit quelle que soit la combinaison de signaux d'entrée. Les éléments de type OR-NOT sont construits de manière similaire. (fig.4.20).

Dans de tels circuits, en raison de la connexion en série des transistors dans l'un des bras, la résistance de sortie augmente dans l'un des états. Par conséquent, ces éléments ont des heures d'activation et de désactivation différentes. Pour l'élément NAND, le temps d'activation est plus long que le temps d'arrêt, et pour l'élément NOR, vice versa.

Riz. 4.19. Implémentation de la fonction 4I-NOT sur CMOS

Riz. 4.20. Implémentation de la fonction 4OR-NOT sur CMOS

En raison de l'impédance d'entrée très élevée, même une charge statique peut créer une tension de claquage. Pour se protéger contre les charges haute tension d'électricité statique, il existe un circuit de protection spécial aux entrées des circuits CMOS (à l'intérieur du microcircuit) (fig. 4.21).

Riz. 4.21. Onduleur CMOS avec circuit de protection de porte ESD

Diodes VD1, VD2 et VD3 protéger l'isolation du portail contre les pannes. Diodes VD4 et VD7 protéger la sortie de l'onduleur contre les pannes entre R et m domaines. Diodes VD5 et VD6 connecté en série entre les rails d'alimentation pour protéger contre l'inversion accidentelle de la polarité de l'alimentation.

Les représentants typiques des circuits CMOS sont des éléments de la série K564, qui se caractérisent par les paramètres suivants :

E P= 3¸15V; U 0= 0,01V (à E P= 5V et Dans=0); U1= 4.99V (à E P= 5V et Dans=0); je 0 dans= 0,2 A ; je 1 dans= 0,2 A ; je p= 0,17 mA (à E P= 10V, F= 100kHz et C n= 50pF); t s= 80ns ; je suis à 0= 0.9mA (à U 0 sur= 0,5V et E P= 10V); je 1 sur= 0.9mA (à U 1 sur=E P-0,5 V et E P= 10V); Cn = 200pF ; Dans= 12pF.

Une expérience individuelle (UIRS) nécessite une attention particulière en préparation.

CMOS, Complémentaire-symétrie / semi-conducteur métal-oxyde ) - technologie de construction de circuits électroniques. La technologie CMOS utilise transistors à effet de champ avec une grille isolée avec des canaux de conductivité différente. Caractéristique distinctive Circuits CMOS versus technologies bipolaires ( TTL , ALS etc.) est une consommation d'énergie très faible en mode statique (dans la plupart des cas, on peut supposer que l'énergie n'est consommée que lors de la commutation d'état). Une particularité de la structure CMOS par rapport aux autres structures MOS ( N-MOS, P-MOS) est la présence de transistors à effet de champ à canal n et p; en conséquence, les circuits CMOS sont plus rapides et moins économes en énergie, mais ils sont plus complexes processus technologique fabrication et densité d'emballage inférieure.La grande majorité des logiques modernes microcircuits, comprenant, processeurs utiliser des circuits CMOS.

Histoire

Les premiers circuits CMOS étaient très vulnérables aux décharge électrostatique... Maintenant, ce problème a été en grande partie résolu, mais lors de l'installation de microcircuits CMOS, il est recommandé de prendre des mesures pour éliminer les charges électriques.

Pour la fabrication de grilles en cellules CMOS en amont, aluminium... Plus tard, dans le cadre de l'émergence de la technologie dite auto-compatible, qui prévoyait l'utilisation de l'obturateur non seulement comme élément structurel, mais en même temps que des masques lors de l'obtention de régions drain-source, ils ont commencé à utiliser silicium polycristallin.

La technologie

Schéma 2I-NOT

Par exemple, considérons le circuit d'une porte 2I-NOT, construit en utilisant la technologie CMOS.

- Si un niveau élevé est appliqué aux deux entrées A et B, les deux transistors au bas du circuit sont ouverts et les deux supérieurs sont fermés, c'est-à-dire que la sortie est connectée à la terre.

- Si un niveau bas est appliqué à au moins une des entrées, le transistor correspondant sera ouvert en haut et fermé en bas. Ainsi, la sortie sera connectée à la tension d'alimentation et déconnectée de la terre.

Il n'y a pas de résistances de charge dans le circuit, donc dans un état statique, seuls les courants de fuite traversent les transistors fermés à travers le circuit CMOS, et la consommation d'énergie est très faible. Lors de la commutation, l'énergie électrique est principalement dépensée pour la charge conteneurs grilles et conducteurs, de sorte que la puissance consommée (et dissipée) soit proportionnelle à la fréquence de ces commutations (par exemple, fréquence d'horloge processeur).

Série de puces CMOS logiques de production étrangère

Série de microcircuits CMOS logiques de production nationale

- Sur les transistors CMOS (CMOS) :

- 164, 176, 561 et 564 correspondent à la série 4000, mais 164 et 176 n'ont qu'une alimentation 9V ;

- Série 1554 - 74AC ;

- 1561 - série 4000B ;

- Série 1564 - 74HC ;

- 1594 - série 74ACT ;

- 5564 - Série 74HCT;