Conférence. Processeurs de fabrication

Microprocesseur est un circuit intégré formé sur un petit cristal de silicium. Le silicium est utilisé dans les microcircuits du fait qu'il possède des propriétés semi-conductrices : sa conductivité électrique est supérieure à celle des diélectriques, mais inférieure à celle des métaux. Le silicium peut être fabriqué à la fois comme isolant qui empêche le mouvement des charges électriques et comme conducteur - alors charges électriques y passera librement. La conductivité du semi-conducteur peut être contrôlée en introduisant des impuretés.

Microprocesseur contient des millions de transistors reliés entre eux par les conducteurs les plus fins en aluminium ou en cuivre et utilisés pour le traitement des données. C'est ainsi que se forment les pneus internes. En conséquence, le microprocesseur remplit de nombreuses fonctions - des opérations mathématiques et logiques au contrôle du fonctionnement d'autres microcircuits et de l'ensemble de l'ordinateur.

L'un des principaux paramètres du microprocesseur est la fréquence du cristal, qui détermine le nombre d'opérations par unité de temps, la fréquence de fonctionnement bus système, la quantité de cache SRAM interne. Le processeur est marqué par la fréquence du cristal. La fréquence du cristal est déterminée par la fréquence de commutation des transistors de l'état fermé à l'état ouvert. La capacité d'un transistor à commuter plus rapidement est déterminée par la technologie de fabrication des plaquettes de silicium à partir desquelles les puces sont fabriquées. La dimension du processus technologique détermine la taille du transistor (son épaisseur et sa longueur de grille).

Comment sont fabriqués les microcircuits

Comme vous le savez d'après le cours de physique de l'école, en électronique moderne, les principaux composants circuits intégrés sont des semi-conducteurs type p et type n(selon le type de conductivité). Semi-conducteur est une substance qui surpasse les diélectriques en conductivité, mais est inférieure aux métaux. Les deux types de semi-conducteurs sont à base de silicium (Si), qui sous sa forme pure (ce qu'on appelle le semi-conducteur intrinsèque) ne conduit pas bien électricité, cependant, l'ajout (insertion) d'une certaine impureté dans le silicium permet de changer radicalement ses propriétés conductrices. Il existe deux types de mixins : donneur et accepteur.

Mélange donneur conduit à la formation de semi-conducteurs de type n avec une conductivité de type électronique, et accepteur - à la formation de semi-conducteurs de type p avec une conductivité de type trou. Les contacts des semi-conducteurs p et n vous permettent de former des transistors - le principal éléments structurels microcircuits modernes. De tels transistors, appelés transistors CMOS, peuvent être dans deux états de base : ouvert, lorsqu'ils conduisent le courant électrique, et fermé, lorsqu'ils ne conduisent pas le courant électrique. Étant donné que les transistors CMOS sont les principaux éléments des microcircuits modernes, parlons-en plus en détail.

Lorsqu'ils parlent de processeurs Intel, ils utilisent souvent des concepts spécifiques tels que le processus technologique de 0,13 micron, et dans Ces derniers temps- Processus technologique 90nm. Par exemple, il est d'usage de dire que les nouveaux Processeur Intel Le Pentium 4 avec noyau Northwood est fabriqué à l'aide de la technologie 0,13 micron, et la prochaine génération de processeurs sera basée sur un processus technologique de 90 nanomètres. Quelle est la différence entre ces processus technologiques et comment cela affecte-t-il les capacités des processeurs eux-mêmes ?

Comment fonctionne un transistor CMOS

Le transistor CMOS de type n le plus simple a trois électrodes : source, grille et drain... Le transistor lui-même est fabriqué dans un semi-conducteur de type p avec une conductivité de trou, et des semi-conducteurs de type n avec une conductivité électronique sont formés dans les régions de drain et de source. Naturellement, en raison de la diffusion des trous de la région p vers la région n et de la diffusion inverse des électrons de la région n vers la région p, des couches appauvries (couches dans lesquelles il n'y a pas de porteurs de charge majeurs) se forment aux frontières des transitions des régions p et n. A l'état normal, c'est-à-dire lorsqu'aucune tension n'est appliquée à la grille, le transistor est dans un état "bloqué", c'est-à-dire qu'il n'est pas capable de conduire le courant de la source au drain. La situation ne change pas, même si on applique une tension entre le drain et la source (dans ce cas, on ne prend pas en compte les courants de fuite provoqués par le mouvement sous l'influence des champs électriques générés de porteurs de charge minoritaires, que c'est-à-dire des trous pour la région n et des électrons pour la région p).

Cependant, si un potentiel positif est appliqué à la grille (Fig. 1), la situation changera radicalement.

Riz. 1. Le principe de fonctionnement d'un transistor CMOS

Sous l'influence du champ électrique de la grille, des trous sont enfoncés profondément dans le semi-conducteur p et des électrons, au contraire, sont attirés dans la région sous la grille, formant un canal enrichi en électrons entre la source et le drain. Lorsqu'une tension positive est appliquée à la grille, ces électrons commencent à se déplacer de la source au drain. Dans ce cas, le transistor conduit le courant - ils disent que le transistor "s'ouvre". Si la tension est retirée de la grille, les électrons cessent d'être attirés dans la région entre la source et le drain, le canal conducteur est détruit et le transistor cesse de faire passer le courant, c'est-à-dire qu'il est "verrouillé". Ainsi, en changeant la tension à la grille, vous pouvez ouvrir ou éteindre le transistor, de la même manière que vous pouvez allumer ou éteindre un interrupteur à bascule classique, contrôlant le passage du courant dans le circuit. C'est pourquoi les transistors sont parfois appelés interrupteurs électroniques. Cependant, contrairement aux conventions interrupteurs mécaniques, les transistors CMOS sont pratiquement sans inertie et peuvent passer de l'état ouvert à l'état fermé des milliards de fois par seconde ! C'est cette caractéristique, c'est-à-dire la capacité de commutation instantanée, qui détermine en fin de compte la vitesse du processeur, qui se compose de dizaines de millions de ces transistors les plus simples.

Ainsi, un circuit intégré moderne se compose de dizaines de millions des transistors CMOS les plus simples.

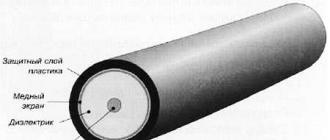

Voici une image la Coupe transversale processeur:

Au-dessus se trouve un couvercle de protection en métal qui, en plus de la fonction de protection, sert également de dissipateur de chaleur - c'est ce que nous enduisons généreusement de pâte thermique lorsque nous installons le refroidisseur. Sous le dissipateur de chaleur se trouve le même morceau de silicium qui effectue toutes les tâches de l'utilisateur. Encore plus bas se trouve un substrat spécial, nécessaire pour le brochage (et pour augmenter la surface des "jambes") afin que le processeur puisse être installé dans un support de carte mère.

La puce elle-même est constituée de silicium, sur lequel se trouvent jusqu'à 9 couches de métallisation (en cuivre) - autant de niveaux sont nécessaires pour que, selon une certaine loi, il soit possible de connecter des transistors situés à la surface du silicium (puisque il est tout simplement impossible de faire tout cela au même niveau). Fondamentalement, ces couches agissent comme des fils de connexion, uniquement à une échelle beaucoup plus petite; pour que les "fils" ne se court-circuitent pas, ils sont séparés par une couche d'oxyde (à faible constante diélectrique).

Arrêtons-nous plus en détail sur le processus de fabrication des microcircuits, dont la première étape est la fabrication de substrats en silicium.

Étape 1. Cultiver des blancs

Étape 2. Candidature film protecteur diélectrique (SiO2)

Étape 3. Application de la résine photosensible

Étape 4. Lithographie

Étape 5. Gravure

Étape 6. Diffusion (implantation ionique)

Étape 7. Pulvérisation et dépôt

Étape 8. Étape finale

Technologies avancées

Onduleurs logiques CMOS (CMDP)

Les microcircuits sur transistors MOS complémentaires (microcircuits CMOS) sont construits à base de transistors MOS à canaux n et p. Le même potentiel d'entrée active le transistor à canal n et bloque le transistor à canal p. Lorsqu'une unité logique est formée, le transistor supérieur est ouvert et le transistor inférieur est fermé. En conséquence, aucun courant ne circule dans le circuit CMOS. Lorsqu'un zéro logique est formé, le transistor inférieur est ouvert et le transistor supérieur est fermé. Et dans ce cas, le courant de l'alimentation ne traverse pas le microcircuit. L'élément logique le plus simple est un onduleur. un inverseur réalisé sur des transistors MOS complémentaires est représenté sur la figure 1.

Figure 1. Schéma de principe d'un inverseur réalisé sur des transistors MOS complémentaires (inverseur CMOS)

En raison de cette caractéristique des microcircuits CMOS, ils ont un avantage sur les types précédemment considérés - ils consomment du courant en fonction de l'entrée fréquence d'horloge... Un graphique approximatif de la dépendance de la consommation de courant d'un microcircuit CMOS, en fonction de la fréquence de sa commutation, est illustré à la figure 2

Figure 2. Dépendance de la consommation de courant d'un microcircuit CMOS sur la fréquence

Éléments logiques CMOS (CMDP) "ET"

Schéma de l'élément logique "AND-NOT" sur les microcircuits CMOS coïncide pratiquement avec le circuit simplifié "ET" sur les touches avec commande électronique que nous avons examiné plus tôt. La différence est que la charge n'est pas connectée au fil commun du circuit, mais à la source d'alimentation. Le schéma de principe de l'élément logique "2I-NOT", réalisé sur des transistors MOS complémentaires (CMOS), est représenté sur la figure 3.

Figure 3. Schéma de principe de l'élément logique "2I-NOT", réalisé sur des transistors MOS complémentaires (CMOS)

Dans ce circuit, un circuit ordinaire pourrait être utilisé dans le bras supérieur, cependant, lorsqu'un faible niveau de signal est formé, le circuit consommerait constamment du courant. Au lieu de cela, des transistors p-MOS sont utilisés comme charge. Ces transistors forment une charge résistive. S'il est nécessaire de former un potentiel élevé en sortie, les transistors s'ouvrent et s'il est faible, ils se ferment.

Dans le circuit de l'élément logique CMOS "ET" illustré à la figure 2, le courant de l'alimentation à la sortie du microcircuit CMOS traversera l'un des transistors si au moins une des entrées (ou les deux à la fois) a un potentiel bas (le niveau logique zéro). Si le niveau d'une unité logique est présent aux deux entrées de l'élément logique CMOS "ET", alors les deux transistors p-MOS seront fermés et un potentiel bas se formera à la sortie du microcircuit CMOS. Dans ce circuit, ainsi que dans le circuit illustré à la figure 1, si les transistors du bras supérieur sont ouverts, les transistors du bras inférieur seront fermés. Par conséquent, dans un état statique, le courant ne sera pas consommé par le microcircuit CMOS de l'alimentation.

La représentation graphique conventionnelle de l'élément logique CMOS "2I-NOT" est illustrée à la figure 4, et la table de vérité est illustrée au tableau 1. Dans le tableau 1, les entrées sont désignées par x 1 et x 2, et la sortie est F.

Figure 4. Représentation graphique conditionnelle de l'élément logique "2I-NOT"

Tableau 1. Table de vérité d'un microcircuit CMOS exécutant "2I-NOT"

| x1 | x2 | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Figure 5. Schéma de principe de l'élément logique "OU-NON", réalisé sur des transistors MOS complémentaires

Dans la porte logique CMOS "2OR-NOT", des transistors p-MOS connectés en série sont utilisés comme charge. Dans celui-ci, le courant de l'alimentation à la sortie du microcircuit CMOS ne circulera que si tous les transistors du bras supérieur sont ouverts, c'est-à-dire si toutes les entrées ont un faible potentiel à la fois (). Si au moins une des entrées a un niveau logique un, le bras supérieur de l'étage push-pull, assemblé sur des transistors CMOS, sera fermé et le courant de l'alimentation ne passera pas à la sortie du microcircuit CMOS .

La table de vérité de l'élément logique "2OR-NOT", mis en œuvre par le microcircuit CMOS, est illustrée dans le tableau 2, et la désignation graphique conventionnelle de ces éléments est illustrée à la figure 6.

Figure 6. Élément "2OU-NON"

Tableau 2. Table de vérité du microcircuit MOS remplissant la fonction logique "2OR-NOT"

| x1 | x2 | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Actuellement, ce sont les microcircuits CMOS qui ont connu le plus grand développement. De plus, il existe une tendance constante à la diminution de la tension d'alimentation de ces microcircuits. La première série de microcircuits CMOS, comme le K1561 (analogue étranger du C4000V), avait une plage de variation de tension d'alimentation assez large (3..18V). Dans le même temps, avec une diminution de la tension d'alimentation pour un microcircuit particulier, sa fréquence de fonctionnement maximale diminue. Plus tard, à mesure que la technologie de production s'améliorait, des microcircuits CMOS améliorés avec de meilleures propriétés de fréquence et une tension d'alimentation inférieure sont apparus, par exemple le SN74HC.

Caractéristiques de l'utilisation des microcircuits CMOS

La première et principale caractéristique des microcircuits CMOS est la haute impédance d'entrée de ces microcircuits. En conséquence, n'importe quelle tension peut être induite à son entrée, y compris la moitié de la tension d'alimentation, et y être stockée pendant une longue période. Lorsque la moitié de l'alimentation est appliquée à l'entrée de l'élément CMOS, les transistors des bras supérieur et inférieur de l'étage de sortie s'ouvrent, en conséquence, le microcircuit commence à consommer un courant inacceptable et peut tomber en panne. Sortir: les entrées des microcircuits numériques CMOS ne doivent jamais rester déconnectées !

La deuxième caractéristique des puces CMOS est qu'elles peuvent fonctionner lorsque l'alimentation est coupée. Cependant, ils fonctionnent souvent de manière incorrecte. Cette caractéristique est liée à la conception de l'étage d'entrée. Le schéma de principe complet de l'onduleur CMOS est illustré à la figure 7.

Figure 7. Schéma de principe complet d'un onduleur CMOS

Les diodes VD1 et VD2 ont été introduites pour protéger l'étage d'entrée des claquages statiques. Dans le même temps, lorsqu'un potentiel élevé est appliqué à l'entrée du microcircuit CMOS, il traversera la diode VD1 jusqu'au bus d'alimentation du microcircuit et, comme il consomme un courant assez faible, le microcircuit CMOS commencera à fonctionner. Cependant, dans certains cas, ce courant peut ne pas être suffisant pour alimenter les microcircuits. En conséquence, la puce CMOS peut ne pas fonctionner correctement. Sortir: si le microcircuit CMOS ne fonctionne pas correctement, vérifiez soigneusement l'alimentation du microcircuit, en particulier le cas conduit. Si la borne d'alimentation négative est mal soudée, son potentiel sera différent du potentiel du fil commun du circuit.

La quatrième caractéristique des microcircuits CMOS est la circulation d'un courant d'impulsion à travers le circuit de puissance lorsqu'il passe de zéro à simple et vice versa. En conséquence, lors du passage des microcircuits TTL aux microcircuits analogiques CMOS, le niveau de bruit augmente fortement. Dans certains cas, cela est important, et il faut abandonner l'utilisation des microcircuits CMOS au profit de l'un ou l'autre des microcircuits BICMOS.

Niveaux logiques CMOS

Les niveaux logiques des microcircuits CMOS diffèrent considérablement de. En l'absence de courant de charge, la tension en sortie du microcircuit CMOS coïncide avec la tension d'alimentation (niveau logique de un) ou avec le potentiel du fil commun (niveau logique de zéro). Avec une augmentation du courant de charge, la tension de l'unité logique peut diminuer jusqu'à 2,8 V (U p = 15 V) par rapport à la tension d'alimentation. Niveau de tension de sortie admissible CMOS numérique microcircuits (série de microcircuits K561) avec une alimentation de cinq volts est illustré à la figure 8.

Figure 8. Niveaux des signaux logiques à la sortie des microcircuits CMOS numériques

Comme mentionné précédemment, la tension à l'entrée d'un microcircuit numérique est généralement autorisée dans une large plage par rapport à la sortie. Pour les microcircuits CMOS convenu d'un stock de 30%. Les limites des niveaux zéro et un logiques pour les microcircuits CMOS avec une alimentation de cinq volts sont illustrées à la figure 9.

Figure 9. Niveaux des signaux logiques à l'entrée des microcircuits CMOS numériques

Lorsque la tension d'alimentation diminue, les limites du zéro logique et de l'unité logique peuvent être déterminées de la même manière (diviser la tension d'alimentation par 3).

Familles CMOS

Les premiers microcircuits CMOS n'avaient pas de diodes de protection à l'entrée, leur installation était donc très difficile. Il s'agit d'une famille de microcircuits de la série K172. La prochaine famille améliorée de puces CMOS, la série K176, a reçu ces diodes de protection. Il est assez répandu à l'heure actuelle. La série K1561 complète le développement de la première génération de puces CMOS. Dans cette famille, une vitesse de 90 ns et une plage de tension d'alimentation de 3 ... 15V ont été atteintes. Étant donné que les équipements étrangers sont actuellement courants, je vais donner un analogue étranger de ces microcircuits CMOS - C4000V.

Un autre développement des microcircuits CMOS était la série SN74HC. Ces microcircuits n'ont pas d'équivalent domestique. Ils ont une vitesse de 27 ns et peuvent fonctionner dans la plage de tension de 2 ... 6 V. Ils coïncident dans le brochage et la plage fonctionnelle avec, mais ne sont pas compatibles avec eux dans niveaux logiques, par conséquent, en même temps, des microcircuits CMOS de la série SN74HCT (analogique domestique - K1564) ont été développés, compatibles avec les microcircuits TTL et aux niveaux logiques.

À cette époque, il y avait une transition vers une alimentation en trois volts. Pour cela, des microcircuits CMOS SN74ALVC ont été développés avec un temps de retard du signal de 5,5 ns et une plage d'alimentation de 1,65 ... 3,6 V. Ces microcircuits sont également capables de fonctionner avec une alimentation de 2,5 volts. Dans ce cas, le temps de retard du signal augmente jusqu'à 9 ns.

La famille de microcircuits CMOS la plus prometteuse est actuellement considérée comme la famille SN74AUC avec un temps de retard du signal de 1,9 ns et une plage d'alimentation de 0,8 ... 2,7 V.

Une série spécifique de microcircuits se caractérise par l'utilisation d'une unité électronique typique - un élément logique de base. Cet élément est à la base de la construction d'une grande variété de appareils électroniques.

Ci-dessous, nous examinerons les caractéristiques des éléments logiques de base de diverses logiques.

Éléments logiques transistor-transistor

Une caractéristique de TTL est l'utilisation de transistors multi-émetteurs. Ces transistors sont conçus de telle sorte que les émetteurs individuels n'interfèrent pas les uns avec les autres. Chaque émetteur a sa propre jonction pn. En première approximation, un multi-émetteur peut être modélisé par un circuit à diodes (voir la ligne pointillée sur la figure 3.27).

Un schéma simplifié d'un élément TTL est illustré à la Fig. 3.27. En remplaçant mentalement un transistor multi-émetteurs par des diodes, nous obtenons un élément de logique diode-transistor "ET-NON". De l'analyse du circuit, on peut conclure que si un niveau de tension bas est appliqué à l'une des entrées ou aux deux entrées, alors la base du transistor T 2 sera nulle et le collecteur du transistor T 2 sera être haut niveau Tension. Si un niveau haut est appliqué aux deux entrées, une grande base traversera la base de T 2 du transistor et il y aura un niveau bas sur le collecteur du transistor T 2, c'est-à-dire que cet élément implémente la fonction NAND :

u dehors = u 1 u 2. L'élément TTL de base contient un transistor multi-émetteurs qui effectue une opération ET logique et un inverseur complexe (Fig. 3.28).

Si un niveau de tension bas est appliqué simultanément à une ou aux deux entrées, alors le transistor multi-émetteur est dans un état de saturation et T 2 est fermé, et par conséquent, le transistor T 4 est également fermé, c'est-à-dire que la sortie sera haute niveau. Si un niveau de tension élevé agit simultanément sur les deux entrées, alors T 2 s'ouvre et entre en mode de saturation, ce qui conduit à l'ouverture et à la saturation du transistor T 4 et au verrouillage du transistor T 3, c'est-à-dire que la fonction NAND est mis en œuvre.

Pour augmenter la vitesse des éléments TTL, des transistors à diodes Schottky (transistors Schottky) sont utilisés.

Élément logique de base TTLSh (par exemple, la série K555)

L'élément NAND est utilisé comme élément de base de la série de microcircuits K555. En figue. 3.29, une un schéma de cet élément est montré, et la désignation graphique conventionnelle est montrée dans la Fig. 3.29, b.

Cela équivaut à la paire ci-dessus d'un transistor conventionnel et d'une diode Schottky. Le transistor VT 4 est un transistor bipolaire classique.

Si les deux tensions d'entrée u in1 et u in2 ont un niveau haut, alors les diodes VD 3 et VD 4 sont fermées, les transistors VT 1, VT 5 sont ouverts et une tension de niveau bas apparaît en sortie. Si au moins une entrée a un niveau bas, alors les transistors VT 1 et VT 5 sont fermés, et les transistors VT 3 et VT 4 sont ouverts, et il existe une tension de niveau bas à l'entrée. Il est utile de noter que les transistors VT 3 et VT 4 forment ce qu'on appelle le composite (circuit Darlington).

Puces TTLSh

Les puces de la série TTLSh K555 se caractérisent par les paramètres suivants :

● alimentation +5 V ;

● tension de sortie de bas niveau - pas plus de 0,4 V ;

● sortie de haut niveau - pas moins de 2,5 V ;

● immunité au bruit - pas moins de 0,3 V ;

● délai moyen de propagation du signal - 20 ns ;

● la fréquence maximale de fonctionnement est de 25 MHz.

Les puces TTLS sont généralement compatibles en niveaux logiques, en immunité au bruit et en alimentation avec les puces TTL. Le temps de retard de propagation du signal des éléments TTLSh est, en moyenne, deux fois inférieur à celui d'éléments TTL similaires.

Caractéristiques des autres logiques

La base de l'élément logique de base de l'ESL est le commutateur de courant. Le circuit du commutateur de courant (Fig. 3.30) est similaire au circuit d'un amplificateur différentiel.

Il faut faire attention au fait que les microcircuits ESL sont alimentés par une tension négative (par exemple, -4,5 V pour la série K1500). Une constante négative est appliquée à la base du transistor VT 2 tension de référence U op. Changer l'entrée u in1 conduit à une redistribution courant continu i e0, donnée par la résistance R e entre les transistors, qui se traduit par une variation des tensions sur leurs collecteurs. Les transistors n'entrent pas en mode de saturation, et c'est l'une des raisons de la grande vitesse des éléments ECL.

Les microcircuits des séries 100, 500 ont les paramètres suivants :

● alimentation - 5,2 V ;

● consommation électrique - 100 mW ;

● facteur de branchement à la sortie - 15 ;

● délai de propagation du signal - 2,9 ns.

Dans les microcircuits n-MOS et p-MOS, des clés sont utilisées, respectivement, sur des transistors MOS à canal n et une charge dynamique (discutée ci-dessus) et sur des transistors MOS à canal p.

A titre d'exemple, considérons un élément logique n-MOS qui implémente la fonction OR-NOT (Fig. 3.31).

Il se compose d'un transistor de charge T 3 et de deux transistors de commande T 1 et T 2. Si les deux transistors T 1 et T 2 sont fermés, alors la sortie est mise à l'état haut. Si l'une ou les deux tensions u 1 et u 2 ont un niveau haut, alors un ou les deux transistors T 1 et T 2 sont ouverts et un niveau bas est défini en sortie, c'est-à-dire la fonction u out = u 1 + u 2 est implémenté.

Pour exclure la consommation d'énergie par un élément logique dans un état statique, des éléments logiques MDP complémentaires (logique CMDP ou CMOS) sont utilisés. Les puces CMOS utilisent des commutateurs MOSFET complémentaires. Ils se distinguent par une immunité élevée au bruit. La logique CMOS est très prometteuse. L'interrupteur complémentaire précédemment considéré est en fait un élément NON (onduleur).

CMOS - élément logique

Considérons CMOS - un élément logique qui implémente la fonction OR-NOT (Fig. 3.32).

Si les tensions d'entrée sont faibles (u 1 et u 2 sont inférieures à la tension de seuil du transistor n-MOS U zi.seuil n), alors les transistors T 1 et T 2 sont fermés, les transistors T 3 et T 4 sont ouverts et la tension de sortie est élevée... Si l'une ou les deux des entrées u 1 et u 2 ont un niveau haut, dépassant le seuil U z. n, alors un ou les deux transistors T 1 et T 2 s'ouvre, et une tension basse est établie entre la source et la grille de l'un ou des deux transistors T 3 et T 4, ce qui conduit au blocage de l'un ou des deux des transistors T 3 et T 4, et donc en sortie est mis à l'état bas. Ainsi, cet élément met en œuvre la fonction u out = u 1 + u 2 et ne consomme de l'énergie de la source d'alimentation que pendant de courtes périodes de temps lorsqu'il est commuté.

La logique d'injection intégrée (IIL ou I 2 L) est basée sur l'utilisation de transistors bipolaires et l'utilisation de circuits et de solutions technologiques originaux. Il se caractérise par une utilisation très économique de la zone cristalline semi-conductrice. Les éléments I 2 L peuvent être mis en œuvre uniquement dans une conception intégrée et n'ont pas d'analogues dans des circuits discrets.  La structure d'un tel élément et son circuit équivalent sont illustrés à la Fig. 3.33, d'où l'on voit que le transistor T 1 (p-n-p) est situé horizontalement, et le multi-collecteur T 2 (n-p n) est situé verticalement. T 1 joue le rôle d'injecteur, fournissant des trous de l'émetteur du transistor T 1 (lorsque le positif lui est appliqué à travers une résistance de limitation) dans la base du transistor T 2. Si u 1 correspond au "0" logique, alors l'injection ne passe pas par la base du transistor multicollecteur T 2 et les courants dans les circuits collecteurs du transistor T 2 ne circulent pas, c'est-à-dire que "1" logique est réglé aux sorties du transistor T 2. A une tension u 1 correspondant au "1" logique, l'injection passe par la base du transistor T 2 et aux sorties du transistor T 2 - zéros logiques.

La structure d'un tel élément et son circuit équivalent sont illustrés à la Fig. 3.33, d'où l'on voit que le transistor T 1 (p-n-p) est situé horizontalement, et le multi-collecteur T 2 (n-p n) est situé verticalement. T 1 joue le rôle d'injecteur, fournissant des trous de l'émetteur du transistor T 1 (lorsque le positif lui est appliqué à travers une résistance de limitation) dans la base du transistor T 2. Si u 1 correspond au "0" logique, alors l'injection ne passe pas par la base du transistor multicollecteur T 2 et les courants dans les circuits collecteurs du transistor T 2 ne circulent pas, c'est-à-dire que "1" logique est réglé aux sorties du transistor T 2. A une tension u 1 correspondant au "1" logique, l'injection passe par la base du transistor T 2 et aux sorties du transistor T 2 - zéros logiques.

Considérez la mise en œuvre de l'élément OR-NOT basé sur l'élément illustré à la Fig. 3.34 (pour simplifier, les autres collecteurs des transistors multicollecteurs T 3 et T 4 ne sont pas représentés sur la figure). Lorsqu'un signal logique "1" est appliqué à une ou aux deux entrées, alors u out correspond à un zéro logique. Si les deux entrées ont des signaux logiques "0", alors la tension u out correspond à un un logique.

La logique basée sur le semi-conducteur à partir d'arséniure de gallium GaAs se caractérise par la vitesse la plus élevée, ce qui est une conséquence de la grande mobilité des électrons (3 ... 6 fois plus que le silicium). Les microcircuits GaAs peuvent fonctionner à des fréquences de l'ordre de 10 GHz ou plus.

Les puces CMOS et leur introduction sur le marché sont un excellent exemple de la complexité et de la confusion dans la priorisation des projets de recherche et développement.

Le fait est que l'effet de champ, qui sous-tend la structure MOS, a été découvert à la fin des années 1920, mais l'ingénierie radio connaissait alors un boom des dispositifs à vide (tubes radio) et les effets trouvés dans les structures cristallines étaient considérés comme peu prometteurs.

Puis, dans les années 40, le transistor bipolaire a été pratiquement redécouvert, et ce n'est qu'alors que de nouvelles recherches et améliorations dans les transistors bipolaires ont montré que cette direction menait à une impasse, les scientifiques se sont souvenus de l'effet de champ.

C'est ainsi qu'est apparu le transistor MOS, puis les microcircuits CMOS. Lettre À au début de l'abréviation signifie complémentaire, c'est-à-dire complémentaire. En pratique, cela signifie que les microcircuits utilisent des paires de transistors avec exactement les mêmes paramètres, mais un transistor a une grille de type n et l'autre transistor a une grille de type p. D'une manière étrangère, les microcircuits CMOS sont appelés CMOS(Oxyde métallique semi-conducteur complémentaire). Les abréviations KMDP, K-MOP sont également utilisées.

Parmi les transistors classiques, un exemple de paire complémentaire est les transistors KT315 et KT361.

Tout d'abord, la série K176 basée sur des transistors à effet de champ est apparue sur le marché des composants radio-électroniques, et en tant que développement ultérieur de cette série, la série K561, qui est devenue très populaire, a été développée. Cette série comprend un grand nombre de puces logiques.

Étant donné que les transistors à effet de champ ne sont pas aussi critiques pour la tension d'alimentation que les transistors bipolaires, cette série est alimentée par une tension de +3 à + 15V. Cela permet à cette série d'être largement utilisée dans divers appareils, y compris ceux alimentés par batterie. De plus, les appareils montés sur des microcircuits de la série K561 consomment très peu de courant. Et pas étonnant, car la base des microcircuits CMOS est un transistor MOS à effet de champ.

Par exemple, le microcircuit K561TP2 contient quatre bascules RS et consomme un courant de 0,14 mA, et un microcircuit similaire de la série K155 consomme au moins 10 - 12 mA. Les microcircuits basés sur des structures CMOS ont une impédance d'entrée très élevée, pouvant atteindre 100 mégohms ou plus, leur capacité de charge est donc assez grande. À la sortie d'un microcircuit, vous pouvez connecter les entrées de 10 à 30 microcircuits. Pour les microcircuits TTL, une telle charge provoquerait une surchauffe et une panne.

Par conséquent, la conception de nœuds sur des microcircuits utilisant des transistors CMOS permet d'utiliser des solutions de circuits plus simples que lors de l'utilisation de microcircuits TTL.

À l'étranger, l'analogue le plus courant de la série K561 est étiqueté CD4000. Par exemple, le CD4011 étranger correspond au microcircuit K561LA7.

En utilisant des microcircuits de la série K561, il ne faut pas oublier certaines des nuances de leur fonctionnement. Il ne faut pas oublier que bien que les microcircuits soient opérationnels dans une large plage de tension, lorsque la tension d'alimentation diminue, l'immunité au bruit diminue et l'impulsion "s'étale" légèrement. C'est-à-dire que plus la tension d'alimentation est proche du maximum, plus les fronts d'impulsion sont raides.

La figure montre un élément de base classique (porte) qui inverse le signal d'entrée (élément NON). C'est-à-dire que si une unité logique arrive à l'entrée, alors un zéro logique est supprimé de la sortie et vice versa. Une paire complémentaire de transistors de type grille "n" et "p" est clairement représentée ici.

La figure suivante montre l'élément de base 2I - NOT. On voit clairement que les résistances présentes dans un élément TTL similaire du microcircuit sont ici absentes. À partir de deux de ces éléments, il est facile d'obtenir un déclencheur, et à partir d'une série séquentielle de déclencheurs, il existe une route directe vers les compteurs, les registres et les dispositifs de mémoire.

Avec toutes les qualités positives des circuits intégrés de la série K561, ils présentent bien sûr des inconvénients. Premièrement, en termes de fréquence de fonctionnement maximale, les microcircuits CMOS sont nettement inférieurs aux microcircuits à logique différente et fonctionnant sur des transistors bipolaires.

La fréquence à laquelle la série K561 fonctionne en toute confiance ne dépasse pas 1 MHz. Pour faire correspondre les microcircuits basés sur des structures MOS avec d'autres séries, par exemple TTL, des convertisseurs de niveau K561PU4, K561LN2 et autres sont utilisés. Ces microcircuits synchronisent également la vitesse, qui peut différer d'une série à l'autre.

Mais le plus gros inconvénient des microcircuits sur des structures MOS complémentaires est la plus forte sensibilité du microcircuit à l'électricité statique. Par conséquent, les usines et les laboratoires sont équipés de lieux de travail spéciaux. Sur la table, tous les travaux sont effectués sur une tôle, qui est connectée à un bus de masse commun. Le corps du fer à souder et le bracelet métallique porté sur la main de l'ouvrier sont connectés à ce bus.

Certains microcircuits sont mis en vente emballés dans du papier d'aluminium, ce qui court-circuite tous les fils entre eux. Lorsqu'on travaille à la maison, il est également nécessaire de trouver un moyen pour que la charge statique s'évacue au moins sur le tuyau de chauffage. Lors de l'installation, les câbles d'alimentation sont d'abord soudés, puis tout le reste.

Riz. 16.10.

La différence fondamentale entre les circuits CMOS et la technologie nMOS est qu'il n'y a pas de résistances actives dans le circuit. Une paire de transistors avec différents types canaliser. Les transistors avec un canal de type p sont connectés par un substrat à une source d'alimentation, par conséquent, la formation d'un canal en eux se produira avec une différence de potentiel suffisamment grande entre le substrat et la grille, et le potentiel à la grille doit être négatif par rapport au substrat. Cette condition est assurée en appliquant un potentiel de masse (c'est-à-dire, logique 0) à la porte. Les transistors avec un canal de type n sont connectés par un substrat à la terre, par conséquent, la formation d'un canal en eux se produira lorsque le potentiel d'alimentation est appliqué à la grille (c'est-à-dire logique 1). Alimentation simultanée de telles paires de transistors avec différents types les canaux d'un zéro logique ou d'une unité logique conduisent au fait qu'un transistor d'une paire sera nécessairement ouvert et l'autre fermé. Ainsi, les conditions sont créées pour connecter la sortie soit à l'alimentation soit à la terre.

Ainsi, dans le cas le plus simple, pour le circuit inverseur (Fig. 16.10) à A = 0, le transistor VT1 sera ouvert et VT2 sera fermé. Par conséquent, la sortie du circuit F sera connectée via le canal VT1 à l'alimentation, ce qui correspond à l'état de l'unité logique : F = 1. Lorsque A = 1, le transistor VT1 sera fermé (sur la grille et le substrat sont les mêmes potentiels), et VT2 est ouvert. Par conséquent, la sortie du circuit F sera connectée à travers le canal du transistor VT2 à la masse. Cela correspond à l'état du zéro logique : F = 0.

L'addition logique (fig.16.11) est effectuée en raison de connexion série canaux p des transistors VT1 et VT2. Lorsqu'au moins un bloc est alimenté, un seul canal n'est pas formé pour ces transistors. Dans le même temps, en raison de la connexion en parallèle de VT3 et VT4, le transistor correspondant est ouvert dans la partie inférieure du circuit, ce qui garantit que la sortie F est connectée à la masse. Il s'avère que F = 0 si au moins un 1 logique est fourni - c'est une règle OU-NON.

Riz. 16.11.

La fonction NAND est réalisée grâce à la connexion en parallèle de VT1 et VT2 dans la partie supérieure du circuit et à la connexion en série de VT3 et VT4 dans la partie inférieure (Fig. 16.12). Lorsqu'au moins une entrée zéro est appliquée, un seul canal n'est pas formé sur VT3 et VT4, la sortie sera déconnectée de la terre. En même temps, au moins un transistor en partie haute du circuit (à la grille duquel est appliqué un zéro logique) assurera la connexion de la sortie F à l'alimentation : F = 1 lorsqu'au moins un zéro est appliqué - la règle NAND.

Riz. 16.12.

Bref résumé

En fonction de la élément de base, faire la distinction entre différentes technologies pour la production de circuits intégrés. Les principaux sont TTL sur transistors bipolaires et nMOS et CMOS sur transistors à effet de champ.

Mots clés

technologie nMOS transistors à effet de champ avec un canal de type n induit.

Tampon pour 3 états- la partie de sortie du circuit TTL, offrant la possibilité de passer au troisième état à haute impédance.

Technologie CMOS- Technologie de production IC basée sur transistors à effet de champ avec des canaux des deux types de conductivité électrique.

Collecteur ouvert- une variante de la mise en œuvre de la partie tampon des éléments TTL sans résistance dans le circuit de charge, qui est sortie du circuit.

Circuits de charge résistive- circuits TTL, dans lesquels l'état du circuit tampon est déterminé par l'état non pas d'un, mais de deux transistors.

Logique transistor-transistor- technologie de fabrication de circuits intégrés à base de transistors bipolaires.

Abréviations acceptées

CMOS - Oxyde métallique semi-conducteur complémentaire

Kit d'entraînement

Exercices pour le cours 16

Exercice 1

Option 1 pour l'exercice 1.Dessinez un schéma de principe d'un élément à 3 entrées OU PAS en utilisant la technologie nMOS.

Option 2 pour l'exercice 1.Dessinez un schéma d'une porte NAND à 3 entrées utilisant la technologie nMOS.

Option 3 pour l'exercice 1.Dessinez un schéma d'un élément OR-NOT à 4 entrées utilisant la technologie nMOS.

Exercice 2

Option 1 pour l'exercice 2.Dessinez un schéma de principe d'un élément à 3 entrées OU PAS en utilisant la technologie CMOS.

Option 2 pour l'exercice 2.Dessinez un diagramme schématique d'un élément NAND à 3 entrées utilisant la technologie CMOS.

Option 3 pour l'exercice 2.Dessiner un schéma de principe d'un élément à 4 entrées OR NOT en technologie CMOS.

Exercice #3

Option 1 pour l'exercice 3.Dessiner un schéma d'un élément à 3 entrées OU NON selon la technologie TTL.

Option 2 pour l'exercice 3.Dessinez un schéma d'une porte NAND à 3 entrées utilisant la technologie TTL.

Option 3 pour l'exercice 3.Dessiner un schéma d'un élément à 4 entrées OU NON selon la technologie TTL.

Exercice 4

Option 1 pour l'exercice 4.Dessinez un schéma d'un élément OU à 3 entrées en utilisant la technologie nMOS.

Option 2 pour l'exercice 4.Dessiner un schéma d'un élément I à 3 entrées en technologie nMOS.

Option 3 pour l'exercice 4.Dessiner un schéma d'un élément OU à 4 entrées utilisant la technologie nMOS.

Exercice 5

Option 1 pour l'exercice 5.Dessinez un schéma d'un élément OU à 3 entrées en utilisant la technologie CMOS.

Option 2 pour l'exercice 5.Dessiner un schéma d'un élément à 3 entrées ET selon la technologie CMOS.

Option 3 pour l'exercice 5.Dessinez un schéma d'un élément OU à 4 entrées en utilisant la technologie CMOS.

Exercice #6

Option 1 pour l'exercice 6.Dessinez un schéma d'un élément OU à 3 entrées en utilisant la technologie TTL.

Option 2 pour l'exercice 6.Dessiner un schéma d'un élément I à 3 entrées selon la technologie TTL.

Option 3 pour l'exercice 6.Dessinez un schéma d'un élément OU à 4 entrées en utilisant la technologie TTL.

Exercice 7

Option 1 pour l'exercice 7.Dessinez un schéma d'un élément 2I-OR-NOT en utilisant la technologie TTL.

Option 2 pour l'exercice 7.Dessinez un circuit d'un élément 2I-OR-NOT en utilisant la technologie CMOS.

Option 3 pour l'exercice 7.Dessinez un circuit d'un élément 2I-OR-NOT en utilisant la technologie nMOS.

Exercice 8

Option 1 pour l'exercice 8.Dessinez un schéma d'une porte OR-NOT à 3 entrées avec un tampon à 3 états.

Option 2 pour l'exercice 8.Dessinez un schéma d'une porte NAND à 3 entrées avec collecteur ouvert.

Option 3 pour l'exercice 8.Dessinez une porte OU à 3 entrées avec un tampon à 3 états.