Conférence n°3

"Conversion analogique-numérique et numérique-analogique."

Dans les systèmes à microprocesseur, le rôle d'élément d'impulsion est joué par un convertisseur analogique-numérique (ADC) et le rôle d'extrapolateur est joué par un convertisseur numérique-analogique (DAC).

Conversion analogique-numérique consiste à convertir l'information contenue dans un signal analogique en un code numérique . Conversion numérique-analogique est conçu pour effectuer la tâche inverse, c'est-à-dire convertir un nombre représenté sous forme de code numérique en un signal analogique équivalent.

En règle générale, les CAN sont installés dans les circuits de rétroaction des systèmes de contrôle numérique pour convertir les signaux de rétroaction analogiques en codes perçus par la partie numérique du système. Que. Les CAN remplissent plusieurs fonctions, telles que : l'échantillonnage temporel, la quantification de niveau, l'encodage. Un schéma fonctionnel généralisé de l'ADC est présenté sur la figure 3.1.

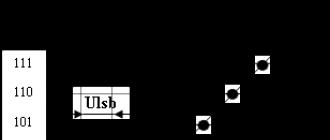

Un signal sous forme de courant ou de tension est fourni à l'entrée de l'ADC, qui est quantifié par niveau pendant le processus de conversion. La caractéristique statique idéale d'un CAN 3 bits est illustrée à la Fig. 3.2.

|

Les signaux d’entrée peuvent prendre n’importe quelle valeur comprise entre – Umax à Umax , et les sorties correspondent à huit (2 3) niveaux discrets. La valeur de la tension d'entrée à laquelle une transition se produit d'une valeur du code de sortie ADC à une autre valeur adjacente est appelée tension de transition d'intercodage. La différence entre deux valeurs adjacentes de transitions intercodes est appelée étape de quantification ou unité du bit le moins significatif (LSB).Le point de départ des caractéristiques de transformation est le point défini par la valeur du signal d'entrée, défini comme

(3.1),

où U 0,1 – tension de la première transition intercode, ULSB – pas de quantification ( LSB – Bit le moins significatif ). la conversion correspond à la tension d'entrée déterminée par la relation

![]() (3.2).

(3.2).

La plage de tension d'entrée ADC est limitée à U 0,1 et U N-1,N appelé Plage de tension d'entrée.

(3.3).

Plage de tension d'entrée et valeur LSB N -bit ADC et DAC sont connectés par le rapport

(3.4).

Tension

(3.5)

appelé tension à pleine échelle ( FSR – Gamme complète ). Généralement, ce paramètre est déterminé par le niveau de sortie de la source de tension de référence connectée au CAN. La taille du pas de quantification ou de l'unité du chiffre le moins significatif, c'est-à-dire égal à

(3.6),

et la valeur de l'unité du chiffre le plus significatif

![]() (3.7).

(3.7).

Comme le montre la figure 3.2, pendant le processus de conversion, une erreur se produit qui ne dépasse pas la moitié de la valeur du bit le moins significatif. U LSB /2.

Il existe différentes méthodes de conversion analogique-numérique, qui diffèrent par leur précision et leur vitesse. Dans la plupart des cas, ces caractéristiques sont antagonistes. Actuellement, des types de convertisseurs tels que les CAN d'approximations successives (équilibrage au niveau des bits), intégrant des CAN, parallèles (Éclair ) ADC, ADC « sigma-delta », etc.

Le schéma fonctionnel de l'ADC à approximations successives est présenté sur la figure 3.3.

Les principaux éléments de l'appareil sont un comparateur (K), un convertisseur numérique-analogique (DAC) et un circuit de commande logique. Le principe de conversion est basé sur une comparaison séquentielle du niveau du signal d'entrée avec les niveaux de signal correspondant à diverses combinaisons du code de sortie et sur la formation du code résultant sur la base des résultats des comparaisons. L'ordre des codes comparés satisfait à la règle des moitiés. Au début de la conversion, le code d'entrée du DAC est défini dans un état dans lequel tous les bits sauf le plus significatif sont 0 et le plus significatif est 1. Avec cette combinaison, une tension égale à la moitié de la plage de tension d'entrée est générée à la sortie DAC. Cette tension est comparée à la tension d'entrée du comparateur. Si le signal d'entrée est supérieur au signal provenant du DAC, alors le bit de poids fort du code de sortie est mis à 1, sinon il est remis à 0. Au cycle d'horloge suivant, le code ainsi partiellement formé est à nouveau reçu à l'entrée du DAC, le bit suivant est mis à un et la comparaison se répète. Le processus se poursuit jusqu'à ce que le bit le moins significatif soit comparé. Que. former N Code de sortie -bit requis N cycles de comparaison élémentaires identiques. Cela signifie que, toutes choses étant égales par ailleurs, les performances d'un tel CAN diminuent avec l'augmentation de sa capacité en bits. Les éléments internes de l'ADC à approximations successives (DAC et comparateur) doivent avoir une précision supérieure à la moitié du bit de poids faible de l'ADC.

Schéma fonctionnel du parallèle (Éclair ) L'ADC est illustré à la Fig. 3.4.

Dans ce cas, la tension d'entrée est immédiatement fournie pour être comparée aux entrées du même nom. N -1 comparateurs. Les entrées opposées des comparateurs sont alimentées par des signaux provenant d'un diviseur de tension de haute précision, qui est connecté à une source de tension de référence. Dans ce cas, les tensions des sorties du diviseur sont réparties uniformément sur toute la plage de modifications du signal d'entrée. L'encodeur prioritaire génère un signal de sortie numérique correspondant au comparateur le plus élevé avec le signal de sortie activé. Que. fournir N -conversion de bits requise 2 N résistances diviseuses et 2 N -1 comparateur. C'est l'une des méthodes de conversion les plus rapides. Cependant, avec une grande capacité, cela nécessite des coûts matériels importants. La précision de toutes les résistances du diviseur et du comparateur doit encore une fois être meilleure que la moitié de la valeur LSB.

Le schéma fonctionnel de l'ADC à double intégration est présenté sur la figure 3.5.

|

Les principaux éléments du système sont un interrupteur analogique composé de clés SW 1, SW 2, SW 3, intégrateur I, comparateur K et compteur C. Le processus de conversion se compose de trois phases (Fig. 3.6).

|

Dans la première phase, la clé est fermée S.W. 1, et les clés restantes sont ouvertes. Grâce à une clé fermée S.W. 1, la tension d'entrée est appliquée à un intégrateur, qui intègre le signal d'entrée sur un intervalle de temps fixe. Passé cet intervalle de temps, le niveau du signal de sortie de l'intégrateur est proportionnel à la valeur du signal d'entrée. Lors de la deuxième étape de transformation, la clé S.W. 1 s'ouvre et la clé S.W. 2 se ferme et un signal de la source de tension de référence est fourni à l'entrée de l'intégrateur. Le condensateur intégrateur est déchargé à partir de la tension accumulée dans le premier intervalle de conversion à un rythme constant proportionnel à la tension de référence. Cette étape se poursuit jusqu'à ce que la tension de sortie de l'intégrateur tombe à zéro, comme indiqué par la sortie du comparateur, qui compare le signal de l'intégrateur à zéro. La durée de la deuxième étape est proportionnelle à la tension d'entrée du convertisseur. Pendant toute la deuxième étape, des impulsions haute fréquence avec une fréquence calibrée sont envoyées au compteur. Que. après la deuxième étape, les relevés du compteur numérique sont proportionnels à la tension d'entrée. Grâce à cette méthode, une très bonne précision peut être obtenue sans imposer des exigences élevées en matière de précision et de stabilité des composants. En particulier, la stabilité de la capacité de l'intégrateur peut ne pas être élevée, puisque les cycles de charge et de décharge se produisent à une vitesse inversement proportionnelle à la capacité. De plus, la dérive du comparateur et les erreurs de décalage sont compensées en démarrant et en terminant chaque étape de conversion à la même tension. Pour améliorer la précision, la troisième étape de conversion est utilisée, lorsque l'intégrateur saisit via une clé S.W. 3, un signal zéro est donné. Étant donné que les mêmes intégrateur et comparateur sont utilisés dans cette étape, la soustraction de la valeur d'erreur de sortie à zéro de la mesure ultérieure peut compenser les erreurs associées aux mesures proches de zéro. Des exigences strictes ne sont pas imposées même sur la fréquence des impulsions d'horloge arrivant au compteur, car un intervalle de temps fixe au premier étage de conversion est formé à partir des mêmes impulsions. Des exigences strictes sont imposées uniquement sur le courant de décharge, c'est-à-dire à la source de tension de référence. L'inconvénient de cette méthode de conversion est sa faible performance.

Les ADC sont caractérisés par un certain nombre de paramètres qui permettent de sélectionner un périphérique spécifique en fonction des exigences du système. Tous les paramètres ADC peuvent être divisés en deux groupes : statiques et dynamiques. Les premiers déterminent les caractéristiques de précision de l'appareil lorsque vous travaillez avec un signal d'entrée constant ou changeant lentement, et les seconds caractérisent les performances de l'appareil comme le maintien de la précision à mesure que la fréquence du signal d'entrée augmente.

Le niveau de quantification situé au voisinage de zéro du signal d'entrée correspond à des tensions de transition intercode de –0,5 U LSB et 0,5 U LSB (le premier ne se produit que dans le cas d'un signal d'entrée bipolaire). Cependant, dans les appareils réels, ces tensions de transition intercode peuvent différer de ces valeurs idéales. L'écart des niveaux réels de ces tensions de transition intercode par rapport à leurs valeurs idéales est appelé erreur de décalage du zéro bipolaire ( Erreur zéro bipolaire ) Et erreur de décalage du zéro unipolaire ( Erreur de décalage zéro ) respectivement. Pour les plages de conversion bipolaire, l'erreur de décalage zéro est généralement utilisée, et pour les plages de conversion unipolaire, l'erreur de décalage unipolaire est généralement utilisée. Cette erreur conduit à un décalage parallèle de la caractéristique de transformation réelle par rapport à la caractéristique idéale le long de l'axe des abscisses (Fig. 3.7).

|

Écart du niveau du signal d'entrée correspondant à la dernière transition intercode par rapport à sa valeur idéale U FSR -1,5 U LSB , appelé erreur à grande échelle ( Erreur de pleine échelle).

Taux de conversion ADC est appelée la tangente de l'angle d'inclinaison de la ligne droite passant par les points de départ et d'arrivée de la caractéristique de transformation réelle. La différence entre les valeurs réelles et idéales du coefficient de conversion est appelée erreur de facteur de conversion ( Erreur de gain ) (Fig. 3.7) Il inclut les erreurs aux extrémités de l’échelle, mais n’inclut pas les erreurs au zéro de l’échelle. Pour la plage unipolaire, elle est définie comme la différence entre l'erreur de pleine échelle et l'erreur de décalage du zéro unipolaire, et pour la plage bipolaire, elle est définie comme la différence entre l'erreur de pleine échelle et l'erreur de décalage du zéro bipolaire. En fait, il s'agit dans tous les cas d'un écart de la distance idéale entre la dernière et la première transition intercode (égale à U FSR-2 U LSB ) de sa valeur réelle.

Les erreurs de décalage zéro et de gain peuvent être compensées en ajustant le préamplificateur ADC. Pour ce faire, vous devez disposer d'un voltmètre avec une précision non pire que 0,1 ULSB . Pour garantir l'indépendance de ces deux erreurs, corrigez d'abord l'erreur de décalage du zéro puis l'erreur du coefficient de conversion.Pour corriger l'erreur de décalage du zéro ADC, vous devez :

1. Réglez la tension d'entrée exactement à 0,5 U LSB ;

2. Ajustez le décalage du préamplificateur ADC jusqu'à ce que l'ADC passe à l'état 00…01.

Pour corriger l'erreur du facteur de conversion il faut :

1. Réglez la tension d'entrée exactement au niveau U FSR -1,5 U LSB ;

2. Ajustez le gain du préamplificateur ADC jusqu'à ce que l'ADC passe à l'état 11...1.

En raison de l'imperfection des éléments du circuit ADC, les pas en différents points des caractéristiques de l'ADC diffèrent les uns des autres en ampleur et ne sont pas égaux. ULSB (Fig. 3.8).

|

Écart de la distance entre les milieux de deux pas de quantification réels adjacents par rapport à la valeur idéale du pas de quantification ULSB appelé non-linéarité différentielle (DNL – Non-linéarité différentielle). Si DNL Plus grand ou égal à ULSB , alors l'ADC peut avoir ce qu'on appelle des « codes manquants » (Fig. 3.3). Cela entraîne une modification locale brutale du coefficient de transmission ADC, ce qui, dans les systèmes de contrôle en boucle fermée, peut entraîner une perte de stabilité.

Pour les applications où il est important de maintenir le signal de sortie avec une précision donnée, il est important que les codes de sortie du CAN correspondent le plus étroitement possible aux tensions de transition inter-codes. L'écart maximal du centre du pas de quantification sur la caractéristique ADC réelle par rapport à la caractéristique linéarisée est appelé non-linéarité intégrale (INL – Non-linéarité intégrale) ouprécision relative (Précision relative) ADC (Fig. 3.9).

|

La caractéristique linéarisée est tracée à travers les points extrêmes de la caractéristique de transformation réelle, après qu'ils ont été calibrés, c'est-à-dire Les erreurs de décalage du zéro et de facteur de conversion ont été éliminées.

Il est presque impossible de compenser les erreurs de non-linéarité différentielle et intégrale par des moyens simples.

Résolution CAN ( Résolution ) est l'inverse du nombre maximum de combinaisons de codes à la sortie de l'ADC

(3.8).

Ce paramètre détermine le niveau minimum du signal d'entrée (par rapport au signal de pleine amplitude) que l'ADC peut percevoir.

La précision et la résolution sont deux caractéristiques indépendantes. La résolution joue un rôle décisif lorsqu'il est important de fournir une plage dynamique donnée du signal d'entrée. La précision est essentielle lorsqu'il est nécessaire de maintenir la variable contrôlée à un niveau donné avec une précision fixe.

Plage dynamique de l'ADC (DR - Plage dynamique ) est le rapport entre le niveau de tension d'entrée maximum perçu et le niveau minimum, exprimé en dB

![]() (3.9).

(3.9).

Ce paramètre détermine la quantité maximale d'informations que l'ADC est capable de transmettre. Donc, pour un ADC 12 bits DR =72 dB.

Les caractéristiques des véritables CAN diffèrent des caractéristiques des appareils idéaux en raison d’éléments non idéaux du dispositif réel. Considérons quelques paramètres caractérisant les vrais ADC.

Rapport signal sur bruit(SNR – Rapport signal/bruit ) est le rapport entre la valeur efficace du signal sinusoïdal d'entrée et la valeur efficace du bruit, qui est définie comme la somme de toutes les autres composantes spectrales jusqu'à la moitié de la fréquence d'échantillonnage, à l'exclusion de la composante continue. Pour le parfait N -bit ADC qui génère uniquement du bruit de quantification RSB , exprimé en décibels, peut être défini comme

(3.10),

(3.10),

où N – Capacité en bits ADC. Donc, pour un ADC 12 bits idéal RSB =74dB. Cette valeur est supérieure à la plage dynamique du même CAN car Le niveau minimum du signal perçu doit être supérieur au niveau de bruit. Cette formule ne prend en compte que le bruit de quantification et ne prend pas en compte les autres sources de bruit qui existent dans les véritables ADC. Par conséquent, les valeurs RSB pour les vrais ADC, il est généralement inférieur à l’idéal. Valeur typique RSB pour un véritable ADC 12 bits, c'est 68-70 dB.

Si le signal d'entrée a un swing moins U FSR , alors la dernière formule doit être ajustée

(3.11),

où KOS est l'atténuation du signal d'entrée, exprimée en dB. Ainsi, si le signal d'entrée d'un CAN 12 bits a une amplitude 10 fois inférieure à la moitié de la tension pleine échelle, alors KOS = -20 dB et SNR = 74 dB – 20 dB = 54 dB.

Signification réelle RSB peut être utilisé pour déterminer le nombre effectif de bits ADC( ENOB – Nombre effectif de bits ). Il est déterminé par la formule

![]() (3.12).

(3.12).

Cet indicateur peut caractériser la capacité décisive réelle d'un véritable ADC. Ainsi, un ADC 12 bits pour lequel RSB =68 dB pour un signal avec KOS = -20 dB est en fait 7 bits ( ENOB =7,68). Valeur ENOB dépend fortement de la fréquence du signal d'entrée, c'est-à-dire La capacité binaire effective de l'ADC diminue avec l'augmentation de la fréquence.

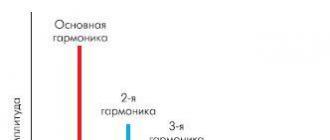

Distorsion harmonique totale ( THD – Distorsion Harmonique Totale ) est le rapport de la somme des valeurs efficaces de toutes les harmoniques supérieures à la valeur efficace de l'harmonique fondamentale

(3.13),

(3.13),

où n généralement limité au niveau 6 ou 9. Ce paramètre caractérise le niveau de distorsion harmonique du signal de sortie ADC par rapport à l'entrée. THD augmente avec la fréquence du signal d’entrée.

Bande de fréquence à pleine puissance ( FPBW – Bande passante pleine puissance ) est la fréquence crête à crête maximale du signal d'entrée à laquelle l'amplitude de la composante fondamentale reconstruite ne diminue pas de plus de 3 dB. À mesure que la fréquence du signal d'entrée augmente, les circuits analogiques de l'ADC n'ont plus le temps de traiter ses modifications avec une précision donnée, ce qui entraîne une diminution du coefficient de conversion de l'ADC aux hautes fréquences.

Temps de prise (Temps de prise ) est le temps nécessaire à l'ADC pour atteindre sa précision nominale après qu'un signal pas à pas d'une amplitude égale à la plage complète du signal d'entrée ait été appliqué à son entrée. Ce paramètre est limité en raison de la vitesse finie des différents nœuds ADC.

En raison de divers types d’erreurs, les caractéristiques d’un véritable CAN ne sont pas linéaires. Si un signal dont le spectre est constitué de deux harmoniques est appliqué à l'entrée d'un appareil à non-linéarités f a et f b , alors dans le spectre du signal de sortie d'un tel appareil, en plus des harmoniques principales, il y aura des sous-harmoniques d'intermodulation avec des fréquences, où m, n =1,2,3,... Les sous-harmoniques du second ordre sont f une + f b , f une - f b , les sous-harmoniques du troisième ordre sont 2 f une + f b , 2 fa - f b , fa +2 f b , f a -2 f b . Si les sinusoïdes d'entrée ont des fréquences similaires, situées près du bord supérieur de la bande passante, alors les sous-harmoniques du deuxième ordre sont très éloignées des sinusoïdes d'entrée et sont situées dans la région des fréquences inférieures, tandis que les sous-harmoniques du troisième ordre ont des fréquences proches de la fréquences d'entrée.

Facteur de distorsion d'intermodulation ( Distorsion intermodulatine ) est le rapport de la somme des valeurs efficaces des sous-harmoniques d'intermodulation d'un certain ordre à la somme des valeurs efficaces des harmoniques fondamentales, exprimée en dB

(3.14).

(3.14).

Toute méthode de conversion analogique-numérique nécessite un temps limité. Sous Temps de conversion ADC ( Temps de conversion ) fait référence à l'intervalle de temps entre le moment où le signal analogique arrive à l'entrée ADC et l'apparition du code de sortie correspondant. Si le signal d'entrée de l'ADC change avec le temps, alors le temps de conversion fini de l'ADC conduit à l'apparition de ce qu'on appelle. erreur d'ouverture(Fig. 3.10).

|

Le signal de début de conversion arrive au moment t 0 , et le code de sortie apparaît en ce moment t1 . Pendant ce temps, le signal d'entrée a réussi à changer de la quantitéD U . Une incertitude surgit : quel niveau de la valeur du signal d'entrée se situe dans la plage U 0 – U 0 + D U correspond à ce code de sortie. Pour maintenir la précision de la conversion au niveau de l'unité du bit le moins significatif, il est nécessaire que pendant le temps de conversion, la variation de la valeur du signal à l'entrée de l'ADC ne soit pas supérieure à la valeur de l'un des bits les moins significatifs. peu significatif

![]() (3.15).

(3.15).

Le changement de niveau de signal pendant la conversion peut être calculé approximativement comme

(3.16),

(3.16),

où Uin – Tension d'entrée ADC, Tc – le temps de conversion. En remplaçant (3.16) dans (3.15) on obtient

![]() (3.17).

(3.17).

Si l'entrée est un signal sinusoïdal avec une fréquence F

![]() (3.18),

(3.18),

alors sa dérivée sera égale

![]() (3.19).

(3.19).

Il prend sa valeur maximale lorsque le cosinus est égal à 1. En substituant (3.9) dans (3.7) dans cette optique, on obtient

![]() , ou

, ou

(3.20)

Le temps de conversion fini de l'ADC conduit à la nécessité de limiter le taux de variation du signal d'entrée. Afin de réduire l'erreur d'ouverture, etc. pour affaiblir la limitation du taux de variation du signal d'entrée ADC à l'entrée du convertisseur, ce qu'on appelle "dispositif de stockage d'échantillonnage" (SSD) ( Unité de suivi/maintien ). Un schéma simplifié de l'UVH est présenté sur la figure 3.11.

|

Cet appareil dispose de deux modes de fonctionnement : le mode échantillonnage et le mode verrouillage. Le mode d'échantillonnage correspond à l'état fermé de la clé S.W. . Dans ce mode, la tension de sortie de l'UVH répète sa tension d'entrée. Le mode accrochage est activé par une commande de la clé d'ouverture S.W. . Dans ce cas, la connexion entre l'entrée et la sortie de l'UVH est interrompue et le signal de sortie est maintenu à un niveau constant correspondant au niveau du signal d'entrée au moment où la commande de fixation est reçue en raison de la charge accumulée sur le condensateur. Ainsi, si vous émettez une commande hold immédiatement avant le début de la conversion ADC, le signal de sortie de l'UVH sera maintenu à un niveau constant pendant toute la durée de conversion. Une fois la conversion terminée, l'UVH passe à nouveau en mode d'échantillonnage. Le fonctionnement d'un véritable UVH est quelque peu différent du cas idéal décrit (Fig. 3.12).

|

![]() (3.21),

(3.21),

où f – fréquence du signal d'entrée, ta – valeur de l'incertitude d'ouverture.

Dans les UVH réels, le signal de sortie ne peut pas rester absolument inchangé pendant un temps de conversion fini. Le condensateur sera progressivement déchargé par le faible courant d'entrée du tampon de sortie. Pour maintenir la précision requise, il est nécessaire que lors de la conversion la charge du condensateur ne change pas de plus de 0,5 ULSB.

Convertisseurs numérique-analogique sont généralement installés à la sortie d'un système à microprocesseur pour convertir ses codes de sortie en un signal analogique fourni à un objet de contrôle continu. La caractéristique statique idéale d'un DAC 3 bits est illustrée à la Fig. 3.13.

|

Point de départ caractéristique défini comme le point correspondant au premier code d'entrée (zéro) U 00…0 . Caractéristique du point final défini comme le point correspondant au dernier code saisi U11…1 . Les définitions de la plage de tension de sortie, du bit le moins significatif de l'unité de quantification, de l'erreur de décalage du zéro et de l'erreur du coefficient de conversion sont similaires aux caractéristiques correspondantes du CAN.

Du point de vue de l'organisation structurelle, les DAC disposent d'une variété d'options beaucoup moins grande pour construire un convertisseur. La structure principale du CAD est ce qu'on appelle. "chaîne Diagramme R -2 R » (Fig. 3.14).

Il est facile de montrer que le courant d’entrée du circuit est I dans = U REF / R , et les courants des maillons successifs de la chaîne sont respectivement Je suis en /2, je suis en /4, je suis en /8, etc. Pour convertir le code numérique d'entrée en courant de sortie, il suffit de collecter tous les courants des bras correspondant à ceux du code d'entrée au point de sortie du convertisseur (Fig. 3.15).

|

Si un amplificateur opérationnel est connecté au point de sortie du convertisseur, alors la tension de sortie peut être déterminée comme

![]() (3.22),

(3.22),

où K – saisir le code numérique, N – Profondeur de bits du DAC.

Tous les DAC existants sont divisés en deux grands groupes : les DAC avec sortie courant et les DAC avec sortie tension. La différence entre eux réside dans l'absence ou la présence d'un étage final sur un amplificateur opérationnel dans la puce DAC. Les DAC avec sortie de tension sont des appareils plus complets et nécessitent moins de composants supplémentaires pour fonctionner. Cependant, la dernière étape, ainsi que les paramètres du circuit forestier, détermine les paramètres dynamiques et de précision du DAC. La mise en œuvre d'un amplificateur opérationnel précis et rapide sur la même puce qu'un DAC est souvent difficile. Par conséquent, la plupart des DAC haute vitesse ont une sortie courant.

Non-linéarité différentielle pour un DAC est défini comme l'écart de la distance entre deux niveaux adjacents du signal analogique de sortie par rapport à la valeur idéale ULSB . Une grande valeur de non-linéarité différentielle peut rendre le DAC non monotone. Cela signifie qu'une augmentation du code numérique entraînera une diminution du signal de sortie dans une partie de la caractéristique (Fig. 3.16). Cela peut conduire à une génération indésirable dans le système.

|

Non-linéarité intégrale pour un DAC, défini comme la plus grande déviation du niveau du signal de sortie analogique par rapport à une ligne droite passant par les points correspondant au premier et au dernier code après leur ajustement.

Temps de prise Le DAC est défini comme le temps pendant lequel le signal de sortie du DAC sera établi à un niveau donné avec une erreur ne dépassant pas 0,5. ULSB après que le code d'entrée soit passé de la valeur 00...0 à la valeur 11...1. Si le DAC dispose de registres d'entrée, alors une certaine partie du temps de stabilisation est due au retard fixe dans le passage des signaux numériques, et seule la partie restante est due à l'inertie du circuit DAC lui-même. Par conséquent, le temps de stabilisation est généralement mesuré non pas à partir du moment où un nouveau code arrive à l'entrée du DAC, mais à partir du moment où le signal de sortie commence à changer, correspondant au nouveau code, jusqu'à ce que le signal de sortie soit établi avec précision. 0,5U LSB (Fig. 3.17).

|

Dans ce cas, le temps de stabilisation détermine la fréquence d'échantillonnage maximale du DAC

(3.23),

où tS – le temps d'établissement.

Les circuits numériques d'entrée du DAC ont une vitesse finie. De plus, la vitesse de propagation des signaux correspondant aux différents bits du code d'entrée n'est pas la même en raison de la variation des paramètres des éléments et des caractéristiques du circuit. En conséquence, les bras du circuit en échelle DAC ne commutent pas de manière synchrone lorsqu'un nouveau code arrive, mais avec un certain retard les uns par rapport aux autres. Cela conduit au fait que dans le diagramme de la tension de sortie du DAC, lors du passage d'une valeur en régime permanent à une autre, des surtensions de différentes amplitudes et directions sont observées (Fig. 3.18).

|

|

Selon l'algorithme de fonctionnement, le DAC est un extrapolateur d'ordre zéro dont la réponse en fréquence peut être représentée par l'expression

(3.24),

(3.24),

Où w s - fréquence d'échantillonnage. La réponse amplitude-fréquence du DAC est illustrée à la Fig. 3.20.

|

Comme on peut le constater, à une fréquence de 0,5w s le signal reconstruit est atténué de 3,92 dB par rapport aux composantes basse fréquence du signal. Il existe ainsi une légère distorsion du spectre du signal reconstruit. Dans la plupart des cas, cette petite distorsion n’affecte pas de manière significative les performances du système. Cependant, dans les cas où une linéarité accrue des caractéristiques spectrales du système est requise (par exemple, dans les systèmes de traitement audio), pour niveler le spectre résultant à la sortie du DAC, il est nécessaire d'installer un filtre de restauration spécial avec une réponse en fréquence de le type x/péché(x).

Convertisseurs analogique-numérique (CAN) – il s’agit d’un dispositif à l’aide duquel se produit le processus de conversion d’une grandeur physique d’entrée en une représentation numérique. La quantité d'entrée peut être le courant, la tension, la résistance, la capacité.

L'ADC est étroitement lié au concept de mesure, qui fait référence au processus de comparaison avec un étalon de la quantité d'entrée mesurée. Autrement dit, la conversion analogique-numérique est considérée comme une mesure de la valeur du signal d'entrée et, par conséquent, les concepts d'erreur de mesure peuvent lui être appliqués.

L'ADC possède un certain nombre de caractéristiques, les principales étant la profondeur de bits et la fréquence de conversion. La profondeur de bits est exprimée en bits et la fréquence de conversion est exprimée en échantillons par seconde. Plus la capacité en bits et la vitesse sont élevées, plus il est difficile d'acquérir les caractéristiques nécessaires et plus le convertisseur est complexe et coûteux.

Le principe, la composition et les schémas structurels de l'ADC dépendent en grande partie de la méthode de conversion.

Classification

Actuellement, un grand nombre de méthodes de conversion tension-code sont connues. Ces méthodes diffèrent considérablement les unes des autres en termes de précision potentielle, de vitesse de conversion et de complexité de mise en œuvre matérielle. En figue. 2 présente la classification des ADC par méthodes de conversion.

Parmi les types de convertisseurs analogique-numérique, les plus populaires sont :

1. CAN de conversion parallèle. Ils ont une faible profondeur de bits et des performances élevées. Le principe de fonctionnement est que le signal d'entrée est fourni aux entrées « positives » des comparateurs et qu'un certain nombre de tensions sont fournies aux entrées « négatives ». Les comparateurs fonctionnent en parallèle ; le temps de retard du circuit est la somme du temps de retard dans un comparateur et du temps de retard dans le codeur. Sur cette base, l'encodeur et le comparateur peuvent être rendus rapides et le circuit atteindra des performances élevées.

2. ADC d'approximation successive. Mesure l'amplitude du signal d'entrée en effectuant une série de « pondérations » ou de comparaisons des valeurs de tension d'entrée et d'un certain nombre de valeurs. Caractérisé par une vitesse de conversion élevée et limité par la précision du DAC interne.

3. ADC avec équilibrage de charge. Le principe de fonctionnement est de comparer la tension d'entrée avec la valeur de tension accumulée par l'intégrateur. Des impulsions sont fournies à l'entrée de l'intégrateur de polarité négative ou positive, en fonction du résultat de la comparaison. En conséquence, la tension de sortie « suit » la tension d’entrée. Caractérisé par une grande précision et de faibles niveaux de bruit.

La conversion analogique-numérique est utilisée partout où un signal analogique doit être reçu et traité sous forme numérique.

- L'ADC fait partie intégrante d'un voltmètre et d'un multimètre numériques.

- Des CAN vidéo spéciaux sont utilisés dans les tuners TV d'ordinateurs, les cartes d'entrée vidéo et les caméras vidéo pour numériser les signaux vidéo. Les entrées microphone et ligne audio des ordinateurs sont connectées à un CAN audio.

- Les ADC font partie intégrante des systèmes d’acquisition de données.

- Des CAN à approximation successive d'une capacité de 8 à 12 bits et des CAN sigma-delta d'une capacité de 16 à 24 bits sont intégrés dans des microcontrôleurs monopuce.

- Des CAN très rapides sont nécessaires dans les oscilloscopes numériques (des CAN parallèles et en pipeline sont utilisés)

- Les balances modernes utilisent des CAN avec une résolution allant jusqu'à 24 bits, qui convertissent le signal directement du capteur à jauge de contrainte (ADC sigma-delta).

- Les ADC font partie des modems radio et autres dispositifs de transmission de données radio, où ils sont utilisés avec un processeur DSP comme démodulateur.

- Les CAN ultra-rapides sont utilisés dans les systèmes d'antennes de stations de base (appelés antennes SMART) et dans les réseaux d'antennes radar.

34. Convertisseurs numérique-analogique, objectif, structure, principe de fonctionnement.

Convertisseur numérique analogique (CAD) - un dispositif permettant de convertir un code numérique (généralement binaire) en un signal analogique (courant, tension ou charge). Les convertisseurs numérique-analogique constituent l'interface entre le monde numérique discret et les signaux analogiques.

Un convertisseur analogique-numérique (ADC) effectue l'opération inverse.

Un DAC audio reçoit généralement un signal numérique modulé par impulsions codées en entrée. La tâche de conversion de divers formats compressés en PCM est effectuée par les codecs respectifs.

DAC appliqué chaque fois qu'il est nécessaire de convertir un signal d'une représentation numérique à une représentation analogique, par exemple dans les lecteurs de CD (Audio CD).

Examinons le principal éventail de problèmes pouvant être attribués aux principes de fonctionnement de différents types. Comptage séquentiel, équilibrage au niveau des bits - que se cache-t-il derrière ces mots ? Quel est le principe de fonctionnement d’un ADC à microcontrôleur ? Nous examinerons ces questions, ainsi qu'un certain nombre d'autres, dans le cadre de l'article. Nous consacrerons les trois premières parties à la théorie générale, et à partir du quatrième sous-titre nous étudierons le principe de leur fonctionnement. Vous pouvez rencontrer les termes ADC et DAC dans diverses publications. Le fonctionnement de ces appareils est légèrement différent, alors ne les confondez pas. Ainsi, l'article passera de la forme analogique à la forme numérique, tandis que le DAC fonctionne à l'envers.

Définition

Avant d’aborder le principe de fonctionnement d’un ADC, découvrons de quel type d’appareil il s’agit. Les convertisseurs analogique-numérique sont des appareils qui convertissent une quantité physique en une représentation numérique correspondante. Le paramètre initial peut être presque n'importe quoi : courant, tension, capacité, résistance, angle de rotation de l'arbre, fréquence d'impulsion, etc. Mais bien sûr, nous ne travaillerons qu’avec une seule transformation. C'est le "code de tension". Le choix de ce format de travail n'est pas accidentel. Après tout, l'ADC (le principe de fonctionnement de cet appareil) et ses caractéristiques dépendent en grande partie du concept de mesure utilisé. Il s'agit du processus de comparaison d'une certaine valeur avec une norme préalablement établie.

Caractéristiques du CAN

Les principaux sont la profondeur de bits et la fréquence de conversion. Le premier est exprimé en bits et le second en coups par seconde. Les convertisseurs analogique-numérique modernes peuvent avoir une résolution de 24 bits ou des vitesses de conversion qui atteignent les unités GSPS. Veuillez noter que l'ADC ne peut vous fournir qu'une seule caractéristique à la fois. Plus leurs indicateurs sont élevés, plus il est difficile de travailler avec l'appareil et l'appareil lui-même coûte plus cher. Mais heureusement, vous pouvez obtenir les indicateurs de profondeur de bits nécessaires en sacrifiant la vitesse de l'appareil.

Types d'ADC

Le principe de fonctionnement varie selon les différents groupes d'appareils. Nous examinerons les types suivants :

- Avec conversion directe.

- Avec approximations successives.

- Avec conversion parallèle.

- Convertisseur analogique-numérique avec équilibrage de charge (delta-sigma).

- Intégration des ADC.

Il existe de nombreux autres types de convoyeurs et de combinaisons qui ont leurs propres caractéristiques particulières et des architectures différentes. Mais les échantillons qui seront considérés dans le cadre de l'article sont intéressants du fait qu'ils jouent un rôle indicatif dans leur niche d'appareils de cette spécificité. Étudions donc le principe de fonctionnement de l'ADC, ainsi que sa dépendance vis-à-vis du périphérique physique.

Convertisseurs analogique-numérique directs

Ils sont devenus très populaires dans les années 60 et 70 du siècle dernier. Ils sont produits sous cette forme depuis les années 80. Ce sont des appareils très simples, voire primitifs, qui ne peuvent se vanter de performances significatives. Leur largeur de bits est généralement de 6 à 8 bits et leur vitesse dépasse rarement 1 GSPS.

Le principe de fonctionnement de ce type d'ADC est le suivant : les entrées positives des comparateurs reçoivent simultanément un signal d'entrée. Une tension d'une certaine amplitude est appliquée aux bornes négatives. Et puis l'appareil détermine son mode de fonctionnement. Cela se fait grâce à la tension de référence. Disons que nous avons un appareil avec 8 comparateurs. Lorsque ½ tension de référence est appliquée, seuls 4 d’entre eux seront activés. L'encodeur prioritaire sera généré et enregistré dans le registre de sortie. Concernant les avantages et les inconvénients, on peut dire que le travail permet de créer des appareils à haut débit. Mais pour obtenir la profondeur de bits requise, vous devez travailler dur.

La formule générale pour le nombre de comparateurs ressemble à ceci : 2^N. Sous N, vous devez mettre le nombre de chiffres. L'exemple évoqué précédemment peut être réutilisé : 2^3=8. Au total, pour obtenir le troisième chiffre, 8 comparateurs sont nécessaires. C’est le principe de fonctionnement des ADC qui ont été créés en premier. Ce n’est pas très pratique, donc d’autres architectures sont apparues par la suite.

Convertisseurs analogique-numérique à approximations successives

Cela utilise un algorithme de « pondération ». En bref, les appareils fonctionnant à l’aide de cette technique sont simplement appelés CAN à comptage en série. Le principe de fonctionnement est le suivant : l'appareil mesure la valeur du signal d'entrée, puis il est comparé aux nombres générés à l'aide d'une certaine méthode :

- La moitié de la tension de référence possible est réglée.

- Si le signal a dépassé la valeur limite du point n°1, il est comparé au nombre qui se situe au milieu entre la valeur restante. Donc, dans notre cas, ce sera les ¾ de la tension de référence. Si le signal de référence n'atteint pas cet indicateur, alors une comparaison sera faite avec une autre partie de l'intervalle selon le même principe. Dans cet exemple, il s’agit de ¼ de tension de référence.

- L’étape 2 doit être répétée N fois, ce qui nous donnera N bits du résultat. Cela est dû à la réalisation d’un nombre N de comparaisons.

Ce principe de fonctionnement permet d'obtenir des dispositifs à vitesse de conversion relativement élevée, qui sont des CAN à approximations successives. Le principe de fonctionnement, comme vous pouvez le constater, est simple et ces appareils sont parfaits pour divers cas.

Convertisseurs A/D parallèles

Ils fonctionnent de la même manière que les appareils série. La formule de calcul est (2^H)-1. Pour le cas considéré précédemment, nous aurons besoin de (2^3)-1 comparateurs. Pour fonctionner, un ensemble spécifique de ces appareils est utilisé, chacun pouvant comparer la tension d'entrée et la tension de référence individuelle. Les convertisseurs analogique-numérique parallèles sont des appareils assez rapides. Mais le principe de conception de ces appareils est tel qu’une puissance importante est nécessaire pour maintenir leur fonctionnalité. Il est donc déconseillé de les utiliser sur batterie.

Convertisseur analogique-numérique avec équilibrage des bits

Il fonctionne selon un schéma similaire à celui de l'appareil précédent. Par conséquent, afin d'expliquer le fonctionnement d'un CAN d'équilibrage au niveau du bit, le principe de fonctionnement pour les débutants sera abordé littéralement en un coup d'œil. Ces dispositifs reposent sur le phénomène de dichotomie. En d'autres termes, une comparaison séquentielle de la valeur mesurée avec une certaine partie de la valeur maximale est effectuée. Des valeurs de ½, 1/8, 1/16 et ainsi de suite peuvent être prises. Par conséquent, un convertisseur analogique-numérique peut réaliser l’ensemble du processus en N itérations (étapes successives). De plus, H est égal à la capacité en bits de l'ADC (regardez les formules données précédemment). Ainsi, on a un gain de temps important, si la rapidité de l'équipement est particulièrement importante. Malgré leur vitesse considérable, ces appareils se caractérisent également par une faible erreur statique.

Convertisseurs analogique-numérique avec équilibrage de charge (delta-sigma)

Il s’agit du type d’appareil le plus intéressant, notamment en raison de son principe de fonctionnement. Elle consiste à comparer la tension d'entrée avec ce qui a été accumulé par l'intégrateur. Des impulsions de polarité négative ou positive sont fournies à l'entrée (tout dépend du résultat de l'opération précédente). Ainsi, on peut dire qu'un tel convertisseur analogique-numérique est un simple système de suivi. Mais ce n'est qu'un exemple de comparaison afin que vous puissiez comprendre l'ADC. Le principe de fonctionnement est systémique, mais pour un fonctionnement efficace de ce convertisseur analogique-numérique, cela ne suffit pas. Le résultat final est un flux infini de uns et de zéros qui traverse le filtre passe-bas numérique. Une certaine séquence de bits en est formée. Une distinction est faite entre les convertisseurs CAN du premier et du deuxième ordre.

Intégration de convertisseurs analogique-numérique

C’est le dernier cas particulier qui sera considéré dans l’article. Nous décrirons ensuite le principe de fonctionnement de ces appareils, mais à un niveau général. Cet ADC est un convertisseur analogique-numérique avec intégration push-pull. Vous pouvez trouver un appareil similaire dans un multimètre numérique. Et ce n’est pas surprenant, car ils offrent une grande précision tout en supprimant bien les interférences.

Concentrons-nous maintenant sur son principe de fonctionnement. Cela consiste dans le fait que le signal d'entrée charge le condensateur pendant un temps déterminé. En règle générale, cette période est une unité de fréquence du réseau qui alimente l'appareil (50 Hz ou 60 Hz). Il peut aussi être multiple. Ainsi, les interférences haute fréquence sont supprimées. Dans le même temps, l'influence de la tension instable de la source d'électricité du réseau sur la précision du résultat est neutralisée.

Lorsque le temps de charge du convertisseur analogique-numérique se termine, le condensateur commence à se décharger à un certain rythme fixe. Le compteur interne de l'appareil compte le nombre d'impulsions d'horloge générées au cours de ce processus. Ainsi, plus la période est longue, plus les indicateurs sont significatifs.

Les CAN à intégration push-pull sont très précis et, de ce fait, ainsi que d'une structure de construction relativement simple, ils sont conçus comme des microcircuits. Le principal inconvénient de ce principe de fonctionnement est sa dépendance à l'indicateur du réseau. N'oubliez pas que ses capacités sont liées à la durée de la période de fréquence de la source d'alimentation.

C’est ainsi que fonctionne un ADC à double intégration. Bien que le principe de fonctionnement de cet appareil soit assez complexe, il fournit des indicateurs de qualité. Dans certains cas, cela est simplement nécessaire.

Nous choisissons un APC avec le principe de fonctionnement dont nous avons besoin

Disons que nous sommes confrontés à une certaine tâche. Quel appareil choisir pour qu’il puisse satisfaire tous nos besoins ? Parlons d’abord de résolution et de précision. Très souvent, ils sont confondus, même si en pratique ils dépendent très faiblement les uns des autres. N'oubliez pas qu'un convertisseur A/D 12 bits peut avoir moins de précision qu'un convertisseur A/D 8 bits. Dans ce cas, la résolution est une mesure du nombre de segments pouvant être extraits de la plage d’entrée du signal mesuré. Ainsi, les CAN 8 bits ont 2 8 = 256 de ces unités.

La précision est l'écart total du résultat de conversion résultant par rapport à la valeur idéale qui devrait être à une tension d'entrée donnée. Autrement dit, le premier paramètre caractérise les capacités potentielles de l'ADC et le second montre ce que nous avons dans la pratique. Par conséquent, un type plus simple (par exemple, des convertisseurs analogique-numérique directs) peut nous convenir, ce qui satisfera les besoins dus à une grande précision.

Pour avoir une idée de ce qui est nécessaire, vous devez d'abord calculer les paramètres physiques et construire une formule mathématique pour l'interaction. Les erreurs statiques et dynamiques y sont importantes, car lors de l'utilisation de différents composants et principes de construction d'un appareil, elles auront des effets différents sur ses caractéristiques. Des informations plus détaillées peuvent être trouvées dans la documentation technique proposée par le fabricant de chaque appareil spécifique.

Exemple

Jetons un coup d'œil à l'ADC SC9711. Le principe de fonctionnement de cet appareil est complexe de par sa taille et ses capacités. D'ailleurs, en parlant de ces derniers, il convient de noter qu'ils sont vraiment diversifiés. Ainsi, par exemple, la fréquence de fonctionnement possible varie de 10 Hz à 10 MHz. En d’autres termes, il peut prélever 10 millions d’échantillons par seconde ! Et l'appareil lui-même n'est pas quelque chose de solide, mais a une structure modulaire. Mais il est généralement utilisé dans des technologies complexes, où il est nécessaire de travailler avec un grand nombre de signaux.

Conclusion

Comme vous pouvez le constater, les ADC reposent sur différents principes de fonctionnement. Cela nous permet de sélectionner les appareils qui répondront à vos besoins, tout en vous permettant de gérer judicieusement les fonds disponibles.

La résolution de l'ADC - le changement minimum dans l'amplitude du signal analogique pouvant être converti par un ADC donné - est associée à sa capacité en bits. Dans le cas d'une seule mesure sans prise en compte du bruit, la résolution est directement déterminée peu profond ADC.

La capacité ADC caractérise le nombre de valeurs discrètes que le convertisseur peut produire en sortie. Dans les CAN binaires, il est mesuré en bits, dans les CAN ternaires, il est mesuré en trits. Par exemple, un CAN binaire 8 bits est capable de produire 256 valeurs discrètes (0...255) car 2 8 = 256 (\style d'affichage 2^(8)=256), un CAN ternaire 8 bits est capable de produire 6561 valeurs discrètes car 3 8 = 6561 (\displaystyle 3^(8)=6561).

La résolution de tension est égale à la différence entre les tensions correspondant au code de sortie maximum et minimum, divisée par le nombre de valeurs discrètes de sortie. Par exemple:

- Exemple 1

- Plage d'entrée = 0 à 10 volts

- Capacité ADC binaire 12 bits : 2 12 = 4096 niveaux de quantification

- Résolution de tension ADC binaire : (10-0)/4096 = 0,00244 volts = 2,44 mV

- Capacité en bits de l'ADC ternaire 12 trit : 3 12 = 531 441 niveau de quantification

- Résolution de tension ADC ternaire : (10-0)/531441 = 0,0188 mV = 18,8 µV

- Exemple 2

- Plage d'entrée = −10 à +10 volts

- CAN binaire 14 bits : 2 14 = 16 384 niveaux de quantification

- Résolution de tension ADC binaire : (10-(-10))/16384 = 20/16384 = 0,00122 volts = 1,22 mV

- Capacité en bits de l'ADC ternaire 14 trit : 3 14 = 4 782 969 niveaux de quantification

- Résolution de tension ADC ternaire : (10-(-10))/4782969 = 0,00418 mV = 4,18 µV

En pratique, la résolution d'un CAN est limitée par le rapport signal/bruit du signal d'entrée. Lorsque l'intensité du bruit à l'entrée ADC est élevée, la distinction entre les niveaux de signaux d'entrée adjacents devient impossible, c'est-à-dire que la résolution se détériore. Dans ce cas, la résolution réellement réalisable est décrite par profondeur de bits efficace (Anglais) nombre effectif de bits, ENOB), ce qui est inférieur à la capacité binaire réelle de l'ADC. Lors de la conversion d'un signal très bruyant, les bits de poids faible du code de sortie sont pratiquement inutiles, car ils contiennent du bruit. Pour atteindre la profondeur de bits déclarée, le rapport signal/bruit du signal d'entrée doit être d'environ 6 dB pour chaque bit de profondeur de bits (6 dB correspond à un double changement du niveau du signal).

Types de conversions

Selon la méthode d'algorithmes utilisée, les ADC sont divisés en :

- Approximation successive

- Série avec modulation sigma-delta

- Étage unique parallèle

- Parallèle à deux étages ou plus (convoyeur)

Les ADC des deux premiers types impliquent l'utilisation obligatoire d'un dispositif d'échantillonnage et de stockage (SSD). Cet appareil permet de stocker la valeur analogique du signal pendant le temps nécessaire pour effectuer la conversion. Sans cela, le résultat de la conversion ADC série ne sera pas fiable. Des CAN intégrés à approximation successive sont produits, contenant tous deux un contrôleur UV et nécessitant un contrôleur UV externe [ ] .

CAN linéaires

La plupart des CAN sont considérés comme linéaires, bien que la conversion analogique-numérique soit intrinsèquement un processus non linéaire (puisque l'opération de mappage d'un espace continu vers un espace discret est une opération non linéaire).

Terme linéaire par rapport à un CAN, signifie que la plage de valeurs d'entrée mappée à une valeur numérique de sortie est liée linéairement à cette valeur de sortie, c'est-à-dire la valeur de sortie k est obtenu avec une plage de valeurs d'entrée allant de

m(k + b) m(k + 1 + b),Où m Et b- quelques constantes. Constante b, en règle générale, a une valeur de 0 ou −0,5. Si b= 0, l'ADC est appelé quantificateur avec étage non nul (taille moyenne), si b= −0,5, alors l'ADC s'appelle quantificateur avec zéro au centre du pas de quantification (mi-marche).

CAN non linéaires

Un paramètre important décrivant la non-linéarité est non-linéarité intégrale (INL) et non-linéarité différentielle (DNL).

Erreur d'ouverture (gigue)

Numérisons un signal sinusoïdal x (t) = Un péché 2 π f 0 t (\displaystyle x(t)=A\sin 2\pi f_(0)t). Idéalement, les mesures sont prises à intervalles réguliers. Cependant, en réalité, l'heure à laquelle l'échantillon est prélevé est sujette à des fluctuations dues à la gigue du front du signal d'horloge ( gigue de l'horloge). En supposant que l'incertitude du moment où la commande est prise Δ t (\displaystyle \Delta t), nous constatons que l'erreur provoquée par ce phénomène peut être estimée comme

E une p ≤ | x ′ (t) Δ t | ≤ 2 UNE π f 0 Δ t (\displaystyle E_(ap)\leq |x"(t)\Delta t|\leq 2A\pi f_(0)\Delta t).L’erreur est relativement faible aux basses fréquences, mais aux fréquences plus élevées, elle peut augmenter considérablement.

L'effet de l'erreur d'ouverture peut être ignoré si son ampleur est relativement faible par rapport à l'erreur de quantification. Ainsi, les exigences suivantes concernant la gigue de front du signal de synchronisation peuvent être définies :

Δt< 1 2 q π f 0 {\displaystyle \Delta t<{\frac {1}{2^{q}\pi f_{0}}}} ,Où q (style d'affichage q)-Capacité ADC.

| Capacité du CAN | Fréquence d'entrée maximale | ||||

|---|---|---|---|---|---|

| 44,1 kHz | 192 kHz | 1 MHz | 10 MHz | 100 MHz | |

| 8 | 28,2 ns | 6,48 ns | 1,24 ns | 124 ch | 12,4 ch |

| 10 | 7,05 ns | 1,62 ns | 311 ch | 31,1 ch | 3,11 ch |

| 12 | 1,76 ns | 405 ch | 77,7 ch | 7,77 ch | 777 FS |

| 14 | 441 ch | 101 ps | 19,4 ch | 1,94 ch | 194 FS |

| 16 | 110 ch | 25,3 ch | 4,86 ch | 486 FS | 48,6 FS |

| 18 | 27,5 ch | 6,32 ch | 1,21 ch | 121 FS | 12,1 FS |

| 24 | 430 fs | 98,8 FS | 19,0 FS | 1,9 FS | 190 ca |

De ce tableau on peut conclure qu'il est conseillé d'utiliser un ADC d'une certaine capacité, compte tenu des restrictions imposées par la gigue du front de synchronisation ( gigue de l'horloge). Par exemple, il est inutile d'utiliser un CAN 24 bits de précision pour enregistrer de l'audio si le système de distribution d'horloge ne peut pas fournir une incertitude ultra-faible.

En général, la qualité du signal d'horloge est extrêmement importante, et pas seulement pour cette raison. Par exemple, d'après la description du microcircuit AD9218(Appareils analogiques) :

Tout CAN haute vitesse est extrêmement sensible à la qualité de l’horloge d’échantillonnage fournie par l’utilisateur. Un circuit track-and-hold est essentiellement un mélangeur. Tout bruit, distorsion ou gigue de synchronisation sur l'horloge est combiné avec le signal souhaité à la sortie analogique-numérique.

Autrement dit, tout CAN haute vitesse est extrêmement sensible à la qualité de la fréquence d'horloge de numérisation fournie par l'utilisateur. Le circuit d'échantillonnage et de stockage est essentiellement un mélangeur (multiplicateur). Tout bruit, distorsion ou gigue d'horloge est mélangé au signal souhaité et envoyé à la sortie numérique.

Fréquence d'échantillonnage

Le signal analogique est une fonction continue du temps ; dans l'ADC, il est converti en une séquence de valeurs numériques. Par conséquent, il est nécessaire de déterminer la fréquence à laquelle les valeurs numériques sont échantillonnées à partir du signal analogique. La fréquence à laquelle les valeurs numériques sont produites est appelée fréquence d'échantillonnage ADC.

Un signal en constante évolution avec une bande spectrale limitée est numérisé (c'est-à-dire que les valeurs du signal sont mesurées sur un intervalle de temps T- période d'échantillonnage), et le signal original peut être exactement reconstruit à partir de valeurs temporelles discrètes par interpolation. La précision de la reconstruction est limitée par l'erreur de quantification. Cependant, selon le théorème de Kotelnikov-Shannon, une reconstruction précise n'est possible que si la fréquence d'échantillonnage est supérieure à deux fois la fréquence maximale dans le spectre du signal.

Étant donné que les véritables CAN ne peuvent pas effectuer de conversion analogique-numérique instantanément, la valeur d'entrée analogique doit être maintenue constante au moins du début à la fin du processus de conversion (cet intervalle de temps est appelé temps de conversion). Ce problème est résolu en utilisant un circuit spécial à l'entrée de l'ADC - un dispositif d'échantillonnage et de maintien (SSD). UVH, en règle générale, stocke la tension d'entrée sur un condensateur, qui est connecté à l'entrée via un interrupteur analogique : lorsque l'interrupteur est fermé, le signal d'entrée est échantillonné (le condensateur est chargé à la tension d'entrée), lorsqu'il est ouvert, le stockage a lieu. De nombreux CAN, réalisés sous forme de circuits intégrés, contiennent un amplificateur intégré.

Alias

Tous les CAN fonctionnent en échantillonnant les valeurs d'entrée à intervalles de temps fixes. Par conséquent, les valeurs de sortie constituent une image incomplète de ce qui est introduit dans l’entrée. Il n'y a aucun moyen de déterminer le comportement du signal d'entrée en examinant les valeurs de sortie. entre des échantillons. Si vous savez que le signal d'entrée change assez lentement par rapport au taux d'échantillonnage, vous pouvez alors supposer que les valeurs intermédiaires entre les échantillons se situent quelque part entre les valeurs de ces échantillons. Si le signal d'entrée change rapidement, aucune hypothèse sur les valeurs intermédiaires du signal d'entrée ne peut être formulée et, par conséquent, il est impossible de restaurer sans ambiguïté la forme du signal d'origine.

Si une séquence de valeurs numériques produite par un CAN est reconvertie sous forme analogique par un convertisseur numérique-analogique quelque part, il est souhaitable que le signal analogique résultant soit une copie aussi précise que possible du signal d'origine. Si le signal d'entrée change plus rapidement que ses échantillons ne sont prélevés, alors une reconstruction précise du signal est impossible et un faux signal sera présent à la sortie du DAC. Les composantes de fausse fréquence du signal (non présentes dans le spectre du signal d'origine) sont appelées alias(fausse fréquence, composante basse fréquence parasite). Le taux de repliement dépend de la différence entre la fréquence du signal et la fréquence d'échantillonnage. Par exemple, une onde sinusoïdale de 2 kHz échantillonnée à 1,5 kHz serait restituée sous la forme d'une onde sinusoïdale de 500 Hz. Ce problème s'appelle alias de fréquence (alias).

Pour éviter le repliement, le signal appliqué à l'entrée ADC doit être filtré passe-bas pour supprimer les composantes spectrales dont la fréquence dépasse la moitié de la fréquence d'échantillonnage. Ce filtre s'appelle anti crénelage(anti-aliasing), son utilisation est extrêmement importante lors de la construction de véritables ADC.

En général, l’utilisation d’un filtre d’entrée analogique n’est pas intéressante uniquement pour cette raison. Il semblerait que le filtre numérique, habituellement utilisé après la numérisation, ait des paramètres incomparablement meilleurs. Mais, si le signal contient des composantes nettement plus puissantes que le signal utile, et suffisamment éloignées de lui en fréquence pour être efficacement supprimées par un filtre analogique, cette solution permet de préserver la plage dynamique de l'ADC : si l'interférence est 10 dB plus fort que le signal, il sera en moyenne gaspillé trois bits de capacité.

Bien que l’alias soit un effet indésirable dans la plupart des cas, il peut être utilisé à bon escient. Par exemple, grâce à cet effet, il est possible d'éviter de down-convertir la fréquence lors de la numérisation d'un signal haute fréquence à bande étroite (voir mixeur). Cependant, pour ce faire, les étages d'entrée analogiques du CAN doivent avoir des paramètres nettement plus élevés que ceux requis pour une utilisation standard du CAN au niveau de l'harmonique fondamentale (vidéo ou basse). Cela nécessite également un filtrage efficace des fréquences hors bande avant l'ADC, car après la numérisation, il n'existe aucun moyen d'identifier et/ou de filtrer la plupart d'entre elles.

Mélanger un signal pseudo-aléatoire (dither)

Certaines caractéristiques de l'ADC peuvent être améliorées en utilisant une technique de mélange de signaux pseudo-aléatoire (tramage anglais). Elle consiste à ajouter du bruit aléatoire (bruit blanc) de faible amplitude au signal analogique d'entrée. En règle générale, l'amplitude du bruit est sélectionnée à un niveau représentant la moitié de la valeur minimale. L'effet de cet ajout est que l'état du MZR passe de manière aléatoire entre les états 0 et 1 avec très peu d'entrées (sans ajouter de bruit, le MZR serait dans l'état 0 ou 1 pendant une longue période). Pour un signal avec un bruit mixte, au lieu de simplement arrondir le signal au chiffre le plus proche, un arrondi aléatoire vers le haut ou vers le bas se produit, et le temps moyen pendant lequel le signal est arrondi à un niveau particulier dépend de la proximité du signal avec ce niveau. . Ainsi, le signal numérisé contient des informations sur l'amplitude du signal avec une résolution meilleure que le MZR, c'est-à-dire que la capacité binaire effective de l'ADC augmente. Le côté négatif de la technique est l'augmentation du bruit dans le signal de sortie. En fait, l’erreur de quantification est répartie sur plusieurs échantillons voisins. Cette approche est plus souhaitable que le simple arrondi au niveau discret le plus proche. Grâce à l'utilisation de la technique de mélange d'un signal pseudo-aléatoire, nous obtenons une reproduction plus précise du signal dans le temps. De petits changements dans le signal peuvent être restaurés à partir de sauts pseudo-aléatoires du LSM par filtrage. De plus, si le bruit est déterministe (l'amplitude du bruit ajouté est connue avec précision à tout moment), alors il peut être soustrait du signal numérisé en augmentant d'abord sa profondeur de bits, éliminant ainsi presque complètement le bruit ajouté.

Les signaux sonores de très petites amplitudes, numérisés sans signal pseudo-aléatoire, sont perçus par l'oreille comme très déformés et désagréables. Lors du mélange d'un signal pseudo-aléatoire, le niveau réel du signal est représenté par la valeur moyenne de plusieurs échantillons consécutifs.

Types d'ADC

Voici les principales méthodes de construction d’ADC électroniques :

- CAN parallèles à conversion directe, les CAN entièrement parallèles, contiennent un comparateur pour chaque niveau de signal d'entrée discret. A tout moment, seuls les comparateurs correspondant à des niveaux inférieurs au niveau du signal d'entrée produisent un signal en excès à leur sortie. Les signaux de tous les comparateurs vont soit directement à un registre parallèle, puis le code est traité par logiciel, soit à un encodeur logique matériel, qui génère le code numérique souhaité dans le matériel en fonction du code à l'entrée de l'encodeur. Les données du codeur sont enregistrées dans un registre parallèle. Le taux d'échantillonnage des CAN parallèles dépend en général des caractéristiques matérielles des éléments analogiques et logiques, ainsi que du taux d'échantillonnage requis. Les CAN à conversion directe parallèle sont les plus rapides, mais ont généralement une résolution ne dépassant pas 8 bits, car ils entraînent des coûts matériels élevés ( 2 n − 1 = 2 8 − 1 = 255 (\displaystyle 2^(n)-1=2^(8)-1=255) comparateurs). Les CAN de ce type ont une très grande taille de puce, une capacité d'entrée élevée et peuvent produire des erreurs à court terme en sortie. Souvent utilisés pour la vidéo ou d’autres signaux haute fréquence, ils sont également largement utilisés dans l’industrie pour surveiller des processus à évolution rapide en temps réel.

- CAN à conversion directe parallèle-série, les CAN partiellement séquentiels, tout en conservant des performances élevées, peuvent réduire considérablement le nombre de comparateurs (jusqu'à k ⋅ (2 n / k − 1) (\displaystyle k\cdot (2^(n/k)-1)), où n est le nombre de bits du code de sortie et k est le nombre de CAN à conversion directe parallèle), nécessaire pour convertir un signal analogique en signal numérique (avec 8 bits et 2 CAN, 30 comparateurs sont nécessaires). Deux ou plusieurs pas de sous-bande (k) sont utilisés. Ils contiennent k CAN à conversion directe parallèle. Les deuxième, troisième, etc. CAN servent à réduire l'erreur de quantification du premier CAN en numérisant cette erreur. La première étape est une conversion grossière (basse résolution). Ensuite, la différence entre le signal d'entrée et le signal analogique correspondant au résultat de la conversion grossière (provenant du DAC auxiliaire auquel le code grossier est fourni) est déterminée. Dans la deuxième étape, la différence trouvée est convertie et le code résultant est combiné avec le code approximatif pour obtenir la valeur numérique avantageuse complète. Ce type d'ADC est plus lent que les ADC à conversion directe parallèle, a une haute résolution et une petite taille de boîtier. Pour augmenter la vitesse du flux de données numérisées en sortie dans les CAN à conversion directe parallèle-série, le fonctionnement en pipeline des CAN parallèles est utilisé.

- Exploitation du pipeline de l'ADC, est utilisé dans les CAN à conversion directe parallèle-série, contrairement au mode de fonctionnement habituel des CAN à conversion directe parallèle-série, dans lequel les données sont transmises après une conversion complète ; en fonctionnement en pipeline, les données de conversion partielle sont transmises dès que car il est prêt jusqu'à la fin de la conversion complète.

- CAN série à conversion directe, CAN entièrement en série (k = n), plus lents que les CAN en parallèle direct et légèrement plus lents que les CAN en série parallèle directe, mais encore plus (jusqu'à n ⋅ (2 n / n − 1) = n ⋅ (2 1 − 1) = n (\displaystyle n\cdot (2^(n/n)-1)=n\cdot (2^(1)-1 )=n), où n est le nombre de bits du code de sortie et k est le nombre de CAN à conversion directe parallèle) réduisez le nombre de comparateurs (avec 8 bits, 8 comparateurs sont nécessaires). Les ADC ternaires de ce type sont environ 1,5 fois plus rapides que les ADC binaires du même type, comparables en nombre de niveaux et en coûts matériels.

- ou ADC avec équilibrage des bits contient un comparateur, un DAC auxiliaire et un registre d'approximations successives. L'ADC convertit le signal analogique en signal numérique en N étapes, où N est la profondeur de bits de l'ADC. A chaque étape, un bit de la valeur numérique souhaitée est déterminé, en commençant par le SZR et en terminant par le LZR. La séquence d'actions pour déterminer le bit suivant est la suivante. Le DAC auxiliaire est mis à une valeur analogique formée à partir des bits déjà déterminés aux étapes précédentes ; le bit qui doit être déterminé à cette étape est mis à 1, les bits de poids faible sont mis à 0. La valeur obtenue au DAC auxiliaire est comparée à la valeur analogique d'entrée. Si la valeur du signal d'entrée est supérieure à la valeur sur le DAC auxiliaire, alors le bit à déterminer reçoit la valeur 1, sinon 0. Ainsi, la détermination de la valeur numérique finale s'apparente à une recherche binaire. Ce type d'ADC a à la fois une vitesse élevée et une bonne résolution. Cependant, en l'absence d'un dispositif d'échantillonnage de stockage, l'erreur sera beaucoup plus importante (imaginez qu'après la numérisation du plus grand chiffre, le signal commence à changer).

- (ADC encodé en delta) contiennent un compteur réversible dont le code est envoyé au DAC auxiliaire. Le signal d'entrée et le signal du DAC auxiliaire sont comparés à l'aide d'un comparateur. Grâce au retour négatif du comparateur vers le compteur, le code du compteur change constamment afin que le signal du DAC auxiliaire diffère le moins possible du signal d'entrée. Après un certain temps, la différence de signal devient inférieure à la valeur minimale et le code du compteur est lu comme signal numérique de sortie de l'ADC. Les CAN de ce type ont une très large plage de signaux d'entrée et une haute résolution, mais le temps de conversion dépend du signal d'entrée, bien qu'il soit limité par le haut. Dans le pire des cas, le temps de conversion est T max =(2 q)/f s, Où q-Capacité ADC, f avec- fréquence du générateur du compteur-horloge. Les CAN à codage différentiel constituent généralement un bon choix pour numériser les signaux du monde réel, car la plupart des signaux des systèmes physiques ne sont pas sujets à des changements brusques. Certains ADC utilisent une approche combinée : codage différentiel et approximation successive ; cela fonctionne particulièrement bien dans les cas où les composantes haute fréquence du signal sont connues pour être relativement petites.

- Comparaison de rampe ADC(certains ADC de ce type sont appelés Intégration des ADC, incluent également les CAN à comptage en série) contiennent un générateur de tension en dents de scie (dans un CAN à comptage en série, un générateur de tension pas à pas composé d'un compteur et d'un DAC), un comparateur et un compteur de temps. Le signal en dents de scie augmente linéairement du niveau inférieur au niveau supérieur, puis retombe rapidement au niveau inférieur. Au moment où commence la montée, le compteur de temps démarre. Lorsque le signal de rampe atteint le niveau du signal d'entrée, le comparateur se déclenche et arrête le compteur ; la valeur est lue sur le compteur et fournie à la sortie ADC. Ce type d'ADC est le plus simple dans sa structure et contient le nombre minimum d'éléments. Dans le même temps, les CAN les plus simples de ce type ont une précision plutôt faible et sont sensibles à la température et à d'autres paramètres externes. Pour augmenter la précision, un générateur de rampe peut être construit autour d'un compteur et d'un DAC auxiliaire, mais cette structure n'a pas d'autres avantages par rapport à CAN à approximations successives Et CAN à codage différentiel.

- ADC avec équilibrage de charge(ceux-ci incluent des CAN avec intégration à deux étages, des CAN avec intégration à plusieurs étages et quelques autres) contiennent un comparateur, un intégrateur de courant, un générateur d'horloge et un compteur d'impulsions. La transformation se déroule en deux étapes ( intégration en deux étapes). Dans un premier temps, la valeur de la tension d'entrée est convertie en un courant (proportionnel à la tension d'entrée), qui est fourni à l'intégrateur de courant dont la charge est initialement nulle. Ce processus se poursuit dans le temps TN, Où T- période du générateur d'horloge, N- constante (grand entier, détermine le temps d'accumulation de charge). Passé ce délai, l'entrée de l'intégrateur est déconnectée de l'entrée ADC et connectée à un générateur de courant stable. La polarité du générateur est telle qu'elle réduit la charge accumulée dans l'intégrateur. Le processus de décharge se poursuit jusqu'à ce que la charge dans l'intégrateur diminue jusqu'à zéro. Le temps de décharge est mesuré en comptant les impulsions d'horloge à partir du moment où la décharge commence jusqu'à ce que l'intégrateur atteigne une charge nulle. Le nombre calculé d'impulsions d'horloge sera le code de sortie ADC. On peut montrer que le nombre d'impulsions n, calculé pendant le temps de décharge, est égal à : n=U saisir N(IR 0) −1 , où U dans-tension d'entrée ADC, N- nombre d'impulsions de l'étage d'accumulation (défini ci-dessus), R.- la résistance de la résistance qui convertit la tension d'entrée en courant, je 0- la valeur du courant issu du générateur de courant stable, déchargeant l'intégrateur au deuxième étage. Ainsi, les paramètres du système potentiellement instables (principalement la capacité du condensateur intégrateur) ne sont pas inclus dans l'expression finale. C'est une conséquence en deux étapes processus : les erreurs introduites aux première et deuxième étapes sont mutuellement soustraites. Il n'y a pas d'exigences strictes même pour la stabilité à long terme du générateur d'horloge et de la tension de polarisation du comparateur : ces paramètres ne doivent être stables que pendant une courte période, c'est-à-dire lors de chaque conversion (pas plus de 2TN). En effet, le principe d'intégration en deux étapes permet de convertir directement le rapport de deux grandeurs analogiques (courant d'entrée et de référence) en un rapport de codes numériques ( n Et N dans les termes définis ci-dessus) sans pratiquement aucune erreur supplémentaire introduite. La largeur typique de ce type d'ADC est de 10 à 18[ ] chiffres binaires. Un avantage supplémentaire est la possibilité de construire des convertisseurs insensibles aux interférences périodiques (par exemple, les interférences du secteur) grâce à l'intégration précise du signal d'entrée sur un intervalle de temps fixe. L'inconvénient de ce type d'ADC est la faible vitesse de conversion. Les CAN d'équilibrage de charge sont utilisés dans les instruments de mesure de haute précision.

- ADC avec conversion intermédiaire en taux de répétition des impulsions. Le signal du capteur passe par un convertisseur de niveau puis par un convertisseur tension-fréquence. Ainsi, l'entrée du circuit logique reçoit elle-même un signal dont la caractéristique est uniquement la fréquence d'impulsion. Le compteur logique reçoit ces impulsions en entrée pendant le temps d'échantillonnage, produisant ainsi à la fin du temps d'échantillonnage une combinaison de codes numériquement égale au nombre d'impulsions reçues par le convertisseur pendant le temps d'échantillonnage. De tels ADC sont assez lents et peu précis, mais sont néanmoins très simples à mettre en œuvre et ont donc un faible coût.

- CAN sigma-delta(également appelés CAN delta-sigma) effectue une conversion analogique-numérique à un taux d'échantillonnage plusieurs fois supérieur à celui requis, et par filtrage ne laisse que la bande spectrale souhaitée dans le signal.

Les CAN non électroniques sont généralement construits sur les mêmes principes.

CAN optiques

Il existe des méthodes optiques [ ] convertissant le signal électrique en code. Ils sont basés sur la capacité de certaines substances à modifier leur indice de réfraction sous l'influence d'un champ électrique. Dans ce cas, un faisceau de lumière traversant une substance change de vitesse ou d'angle de déviation à la limite de cette substance en fonction de la modification de l'indice de réfraction. Il existe plusieurs façons d'enregistrer ces modifications. Par exemple, une ligne de photodétecteurs enregistre la déviation du faisceau et la convertit en un code discret. Divers schémas d'interférence impliquant un faisceau retardé permettent d'évaluer les changements de signal ou de construire des comparateurs de grandeurs électriques.

L'un des facteurs qui augmentent le coût des puces est le nombre de broches, car elles obligent le boîtier de puces à être plus grand et chaque broche doit être fixée à la puce. Pour réduire le nombre de broches, les CAN fonctionnant à de faibles taux d'échantillonnage disposent souvent d'une interface série. L'utilisation d'un CAN avec une interface série permet souvent une densité de conditionnement accrue et une surface de carte plus petite.

Les puces ADC ont souvent plusieurs entrées analogiques connectées dans la puce à un seul ADC via un multiplexeur analogique. Différents modèles de CAN peuvent inclure des dispositifs échantillonneurs-bloqueurs, des amplificateurs d'instrumentation ou des entrées différentielles haute tension et d'autres circuits similaires.

Application de l'ADC à l'enregistrement sonore

Les ADC sont intégrés à la plupart des équipements d'enregistrement audio modernes, car le traitement audio est généralement effectué sur des ordinateurs ; Même lors de l'utilisation d'un enregistrement analogique, un CAN est nécessaire pour convertir le signal en un flux PCM, qui sera enregistré sur le support d'informations.

Les CAN modernes utilisés dans l'enregistrement audio peuvent fonctionner à des fréquences d'échantillonnage allant jusqu'à 192 kHz. De nombreuses personnes impliquées dans ce domaine estiment que cet indicateur est redondant et est utilisé à des fins purement marketing (en témoigne le théorème de Kotelnikov-Shannon). On peut dire qu'un signal audio analogique ne contient pas autant d'informations qu'un signal numérique à une fréquence d'échantillonnage aussi élevée, et souvent l'audio hi-fi utilise une fréquence d'échantillonnage de 44,1 kHz (standard pour les CD) ou 48 kHz (typique de la représentation sonore dans les ordinateurs). Cependant, une large bande simplifie et réduit le coût de mise en œuvre des filtres anti-aliasing, leur permettant d'être réalisés avec moins de liaisons ou avec moins de raideur dans la bande d'arrêt, ce qui a un effet positif sur la réponse en phase du filtre dans la bande passante.

De plus, la bande passante excédentaire de l'ADC lui permet de réduire en conséquence la distorsion d'amplitude qui survient inévitablement en raison de la présence d'un circuit échantillonneur-bloqueur. De telles distorsions (non-linéarité de la réponse en fréquence) ont la forme péché(x)/x [ ] et se réfèrent à la totalité de la bande passante, donc moins la bande passante (par fréquence) est utilisée (occupée par le signal utile), moins ces distorsions sont importantes.

Les convertisseurs analogique-numérique pour l'enregistrement audio ont une large gamme de prix - de 5 000 à 10 000 dollars et plus pour un CAN à deux canaux.

Les CAN pour l'enregistrement audio utilisés dans les ordinateurs peuvent être internes ou externes. Il existe également un progiciel gratuit PulseAudio pour Linux qui vous permet d'utiliser des ordinateurs auxiliaires comme DAC/ADC externes pour l'ordinateur principal avec une latence garantie.

.La plupart des capteurs et actionneurs des systèmes automatiques fonctionnent avec des signaux analogiques. Pour entrer de tels signaux dans un ordinateur, ils doivent être convertis sous forme numérique, c'est-à-dire discrétiser par niveau et par temps. Les ADC résolvent ce problème. Le problème inverse, c'est-à-dire La conversion d'un signal quantifié (numérique) en un signal continu est décidée par le DAC.

Les CAN et DAC sont les principaux dispositifs d'entrée/sortie d'informations dans les systèmes numériques conçus pour traiter des informations analogiques ou contrôler tout processus technologique.

Les caractéristiques les plus importantes de l’ADC et du DAC :

1) Type de valeur analogique entrée dans l'ADC et sortie vers le DAC (tension, courant, intervalle de temps, phase, fréquence, mouvement angulaire et linéaire, éclairage, pression, température, etc.). Les convertisseurs les plus utilisés sont ceux dans lesquels la valeur analogique d'entrée (sortie) est la tension, car La plupart des grandeurs analogiques sont relativement faciles à convertir en tension.

2) Résolution et précision de conversion (la résolution est déterminée par le nombre de bits binaires du code ou le nombre possible de niveaux du signal analogique, la précision est déterminée par le plus grand écart du signal analogique par rapport au signal numérique et vice versa).

3) Performances, déterminées par l'intervalle de temps entre le moment où le signal d'interrogation (démarrage) est envoyé et celui où le signal de sortie atteint une valeur stable (unités de microsecondes, dizaines de nanosecondes)

Tout convertisseur comporte des parties numériques et analogiques. En numérique, les signaux numériques sont codés et décodés, stockés, comptés, comparés numériquement et des signaux de contrôle logiques sont générés. Ils utilisent à cet effet : des décodeurs, des multiplexeurs, des registres, des compteurs, des comparateurs numériques, des éléments logiques.

Dans la partie analogique du convertisseur, des opérations sont effectuées : amplification, comparaison, commutation, addition et soustraction de signaux analogiques. Pour cela, des éléments analogiques sont utilisés : amplificateurs opérationnels, comparateurs analogiques, interrupteurs et interrupteurs, matrices résistives, etc.

Les convertisseurs se présentent sous la forme de circuits intégrés ou LSI numériques et analogiques.